Ip core parameters, System settings – Altera IP Compiler for PCI Express User Manual

Page 44

3–8

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

However, bit 0 of PCIe Address 31:0 has the following special significance:

■

If bit 0 of PCIe Address 31:0 has value 0, the PCI Express memory accessed

through this address page is 32-bit addressable.

■

If bit 0 of PCIe Address 31:0 has value 1, the PCI Express memory accessed

through this address page is 64-bit addressable.

IP Core Parameters

The following sections describe the IP Compiler for PCI Express parameters

System Settings

The first page of the Parameter Settings tab contains the parameters for the overall

system settings.

describes these settings.

The IP Compiler for PCI Express parameter editor that appears in the Qsys flow

provides only the Gen2 Lane Rate Mode, Number of lanes, Reference clock

frequency

, Use 62.5 MHz application clock, and Test out width system settings

parameters. For more information, refer to

“Parameters in the Qsys Design Flow” on

.

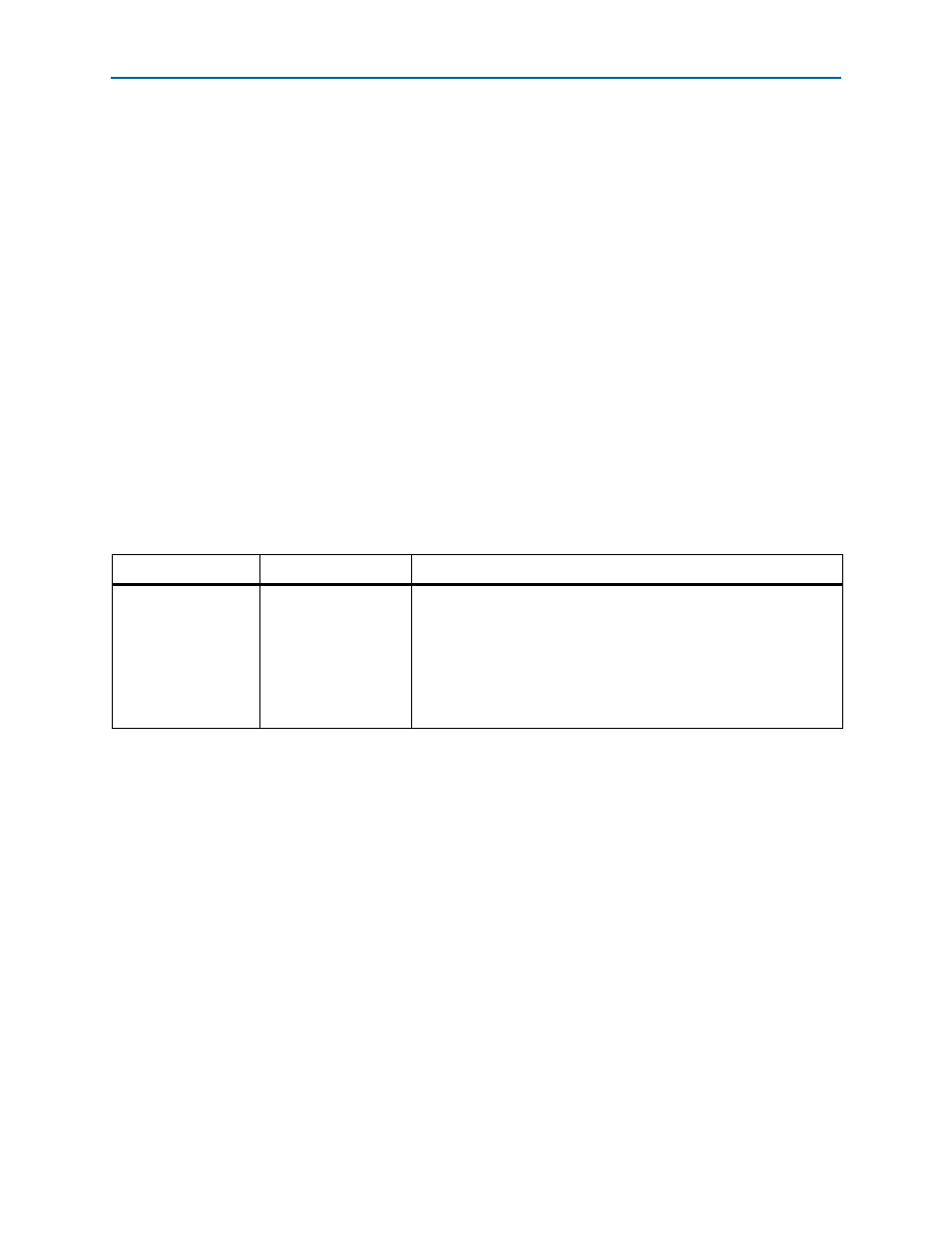

Table 3–9. System Settings Parameters (Part 1 of 4)

Parameter

Value

Description

PCIe Core Type

Hard IP for PCI Express

Soft IP for PCI Express

The hard IP implementation uses embedded dedicated logic to

implement the PCI Express protocol stack, including the physical layer,

data link layer, and transaction layer.

The soft IP implementation uses optimized PLD logic to implement the

PCI Express protocol stack, including physical layer, data link layer, and

transaction layer.

The Qsys design flows support only the hard IP implementation.