Constraining the design – Altera IP Compiler for PCI Express User Manual

Page 32

2–16

Chapter 2: Getting Started

Constraining the Design

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Constraining the Design

The Quartus project directory for the chaining DMA design example is in

<working_dir>\top_examples\chaining_dma\. Before compiling the design using

the Quartus II software, you must apply appropriate design constraints, such as

timing constraints. The Quartus II software automatically generates the constraint

files when you generate the IP Compiler for PCI Express.

describes these constraint files.

If you want to perform an initial compilation to check any potential issues without

creating pin assignments for a specific board, you can do so after running the

following two steps that constrain the chaining DMA design example:

1. To apply Quartus II constraint files, type the following commands at the Tcl

console command prompt:

source ../../top.tcl

r

1

To display the Quartus II Tcl Console, on the View menu, point to Utility

Windows

and click Tcl Console.

2. To add the Synopsys timing constraints to your design, follow these steps:

a. On the Assignments menu, click Settings.

b. Click TimeQuest Timing Analyzer.

c. Under SDC files to include in the project, click the Browse button. Browse to

your <working_dir> to add top.sdc.

d. Click Add.

e. Click OK.

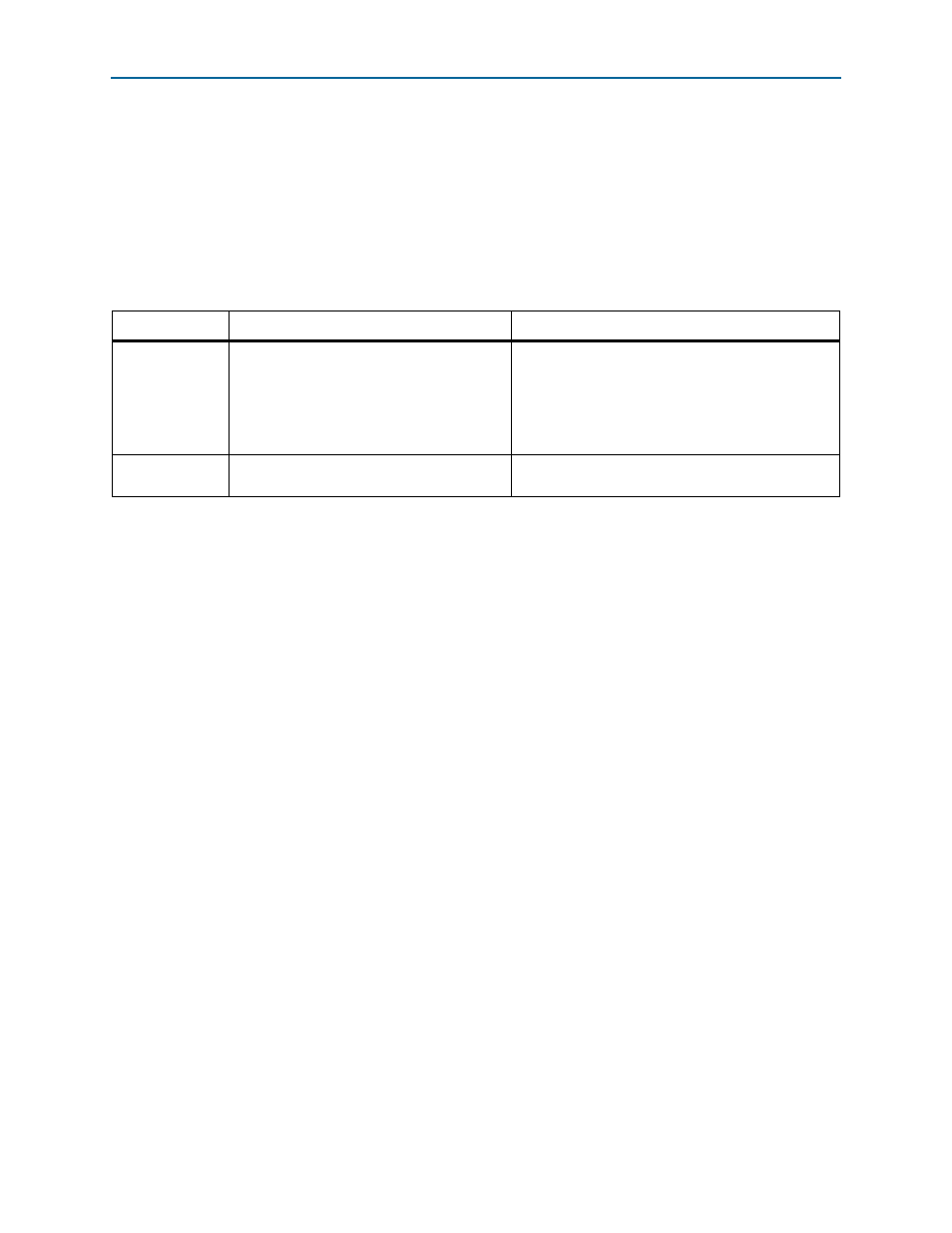

Table 2–8. Automatically Generated Constraints Files

Constraint Type

Directory

Description

General

<working_dir>/<variation>.tcl (top.tcl)

This file includes various Quartus II constraints. In

particular, it includes virtual pin assignments. Virtual

pin assignments allow you to avoid making specific

pin assignments for top-level signals while you are

simulating and not yet ready to map the design to

hardware.

Timing

<working_dir>/<variation>.sdc (top.sdc)

This file is the Synopsys Design Constraints File (.sdc)

which includes timing constraints.