Pci express interrupts for root ports, Configuration space signals—hard ip implementation – Altera IP Compiler for PCI Express User Manual

Page 115

Chapter 5: IP Core Interfaces

5–29

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

PCI Express Interrupts for Root Ports

describes the signals available to a root port to handle interrupts.

Configuration Space Signals—Hard IP Implementation

The hard IP implementation of the configuration space signals is the same for all

devices that support the IP Compiler for PCI Express hard IP implementation.

[3:1]

multiple

message

capable

Multiple message capable: This field is read by system software to determine the

number of requested MSI messages.

■

000: 1 MSI requested

■

001: 2 MSI requested

■

010: 4 MSI requested

■

011: 8 MSI requested

■

100: 16 MSI requested

■

101: 32 MSI requested

■

110: Reserved

[0]

MSI Enable

If set to 0, this IP core is not permitted to use MSI.

Table 5–11. Configuration MSI Control Status Register Field Descriptions (Part 2 of 2)

Bit(s)

Field

Description

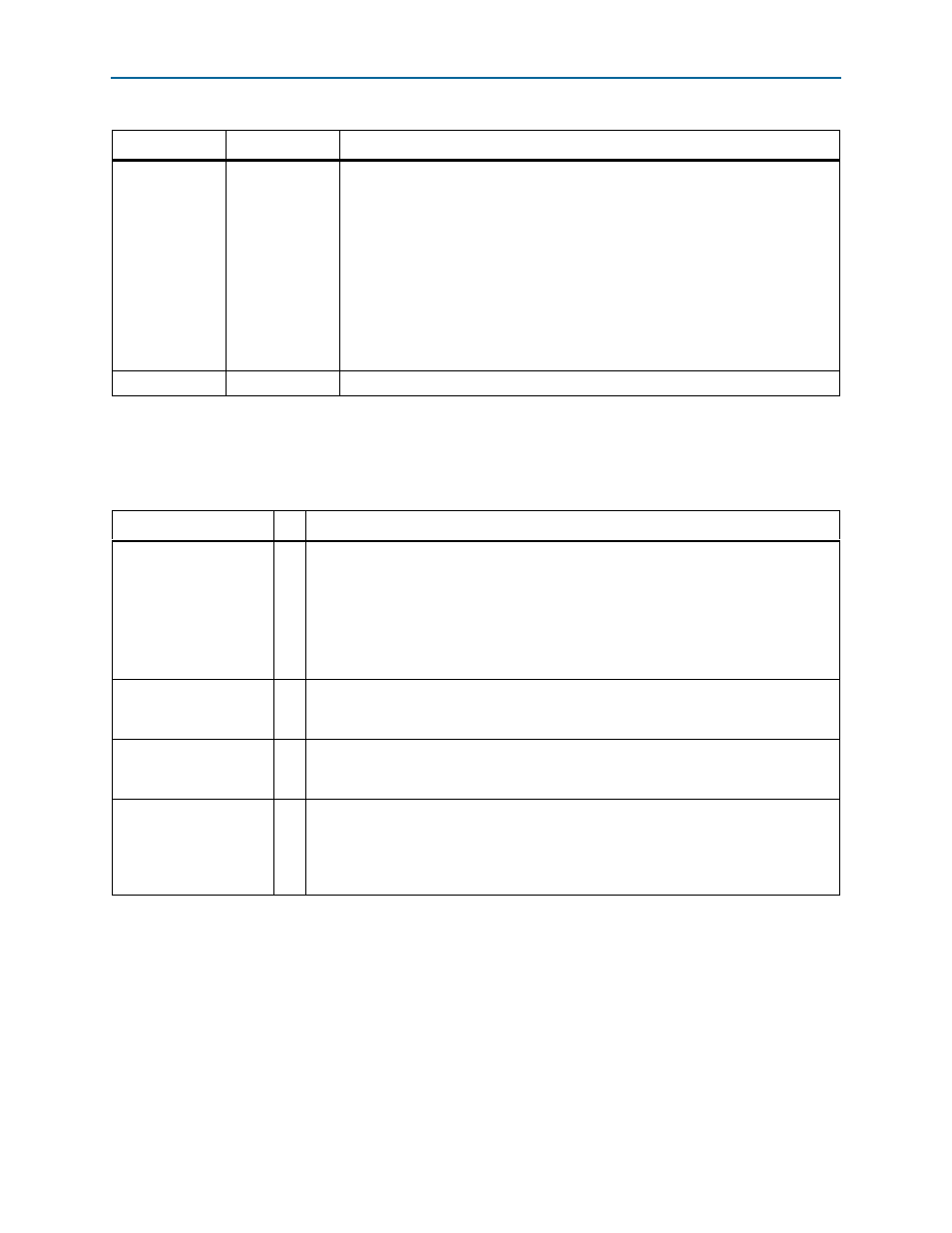

Table 5–12. Interrupt Signals for Root Ports

Signal

I/O

Description

int_status[3:0]

O

These signals drive legacy interrupts to the application layer using a TLP of type Message

Interrupt as follows:

■

int_status[0]: interrupt signal A

■

int_status[1]: interrupt signal B

■

int_status[2]: interrupt signal C

■

int_status[3]: interrupt signal D

aer_msi_num[4:0]

I

Advanced error reporting (AER) MSI number. This signal is used by AER to determine the

offset between the base message data and the MSI to send. This signal is only available

for root port mode.

pex_msi_num[4:0]

I

Power management MSI number. This signal is used by power management and/or hot

plug to determine the offset between the base message interrupt number and the message

interrupt number to send through MSI.

serr_out

O

System Error: This signal only applies to hard IP root port designs that report each system

error detected by the IP core, assuming the proper enabling bits are asserted in the root

control register and the device control register. If enabled, serr_out is asserted for a

single clock cycle when a system error occurs. System errors are described

or 2.0

in the root control register.