Recommended incremental compilation flow, Table b–15 on – Altera IP Compiler for PCI Express User Manual

Page 351

Chapter :

B–33

Recommended Incremental Compilation Flow

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

TX Ports

describes the application-side TX signals.

Recommended Incremental Compilation Flow

When using the incremental compilation flow, Altera recommends that you include a

fully registered boundary on your application. By registering signals, you reserve the

entire timing budget between the application and IP Compiler for PCI Express for

routing.

f

Refer to

in

volume 1 of the Quartus II Handbook.

The following is a suggested incremental compile flow. The instructions cover

incremental compilation for both the Avalon-ST and the descriptor/data interfaces.

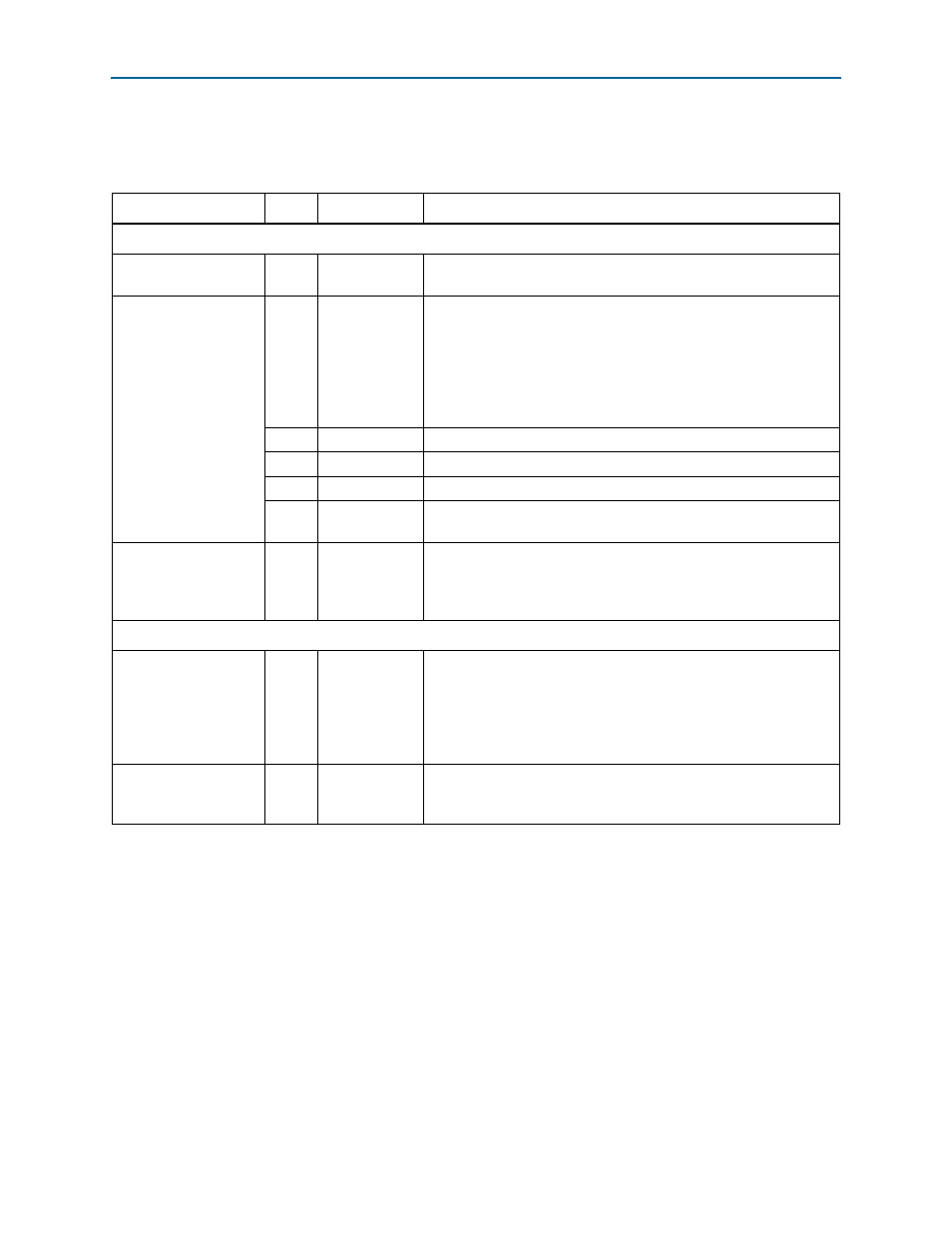

Table B–15. Application-Side TX Signals

Signal

Bit

Subsignals

Description

Avalon-ST TX Interface Signals

tx_st_valid0

Clocks tx_st_data0 into the ICM. The ICM accepts data when

tx_st_valid0

is high.

tx_st_data0

63:0

tx_desc/tx_data

Multiplexed tx_desc0/tx_data0 bus.

1st cycle – tx_desc0[127:64]

2nd cycle – tx_desc0[63:0]

3rd cycle – tx_data0 (if any)

Refer to for information on

tx_data0

.

71:64 Unused

bits

72

tx_eop_flag

Asserts on the last cycle of the packet

73

tx_sop_flag

Asserts on the 1st cycle of the packet

74

tx_err

Same as IP core definition. Refer to

information.

tx_st_ready0

The ICM asserts this signal when it can accept more data. The ICM

deasserts this signal to throttle the data. When the ICM deasserts this

signal, the user application must also deassert tx_st_valid0 within

3 clk cycles.

Other TX Interface Signals

tx_stream_cred0

65:0

Available credits in IP core (credit limit minus credits consumed).

This signal corresponds to tx_cred0 from the IP Compiler for PCI

Express delayed by one system clock cycle. This information can be

used by the application to send packets based on available credits.

Note that this signal does not account for credits consumed in the

ICM. Refer to

for information on tx_cred0.

tx_stream_mask0

Asserted by ICM to throttle Non-Posted requests from application.

When set, application should stop issuing Non-Posted requests in

order to prevent head-of-line blocking.