Altera IP Compiler for PCI Express User Manual

Page 333

Chapter :

B–15

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

describes the advanced data phase signals.

shows the bit information for tx_cred<n>[21:0] for the ×1 and ×4 IP cores.

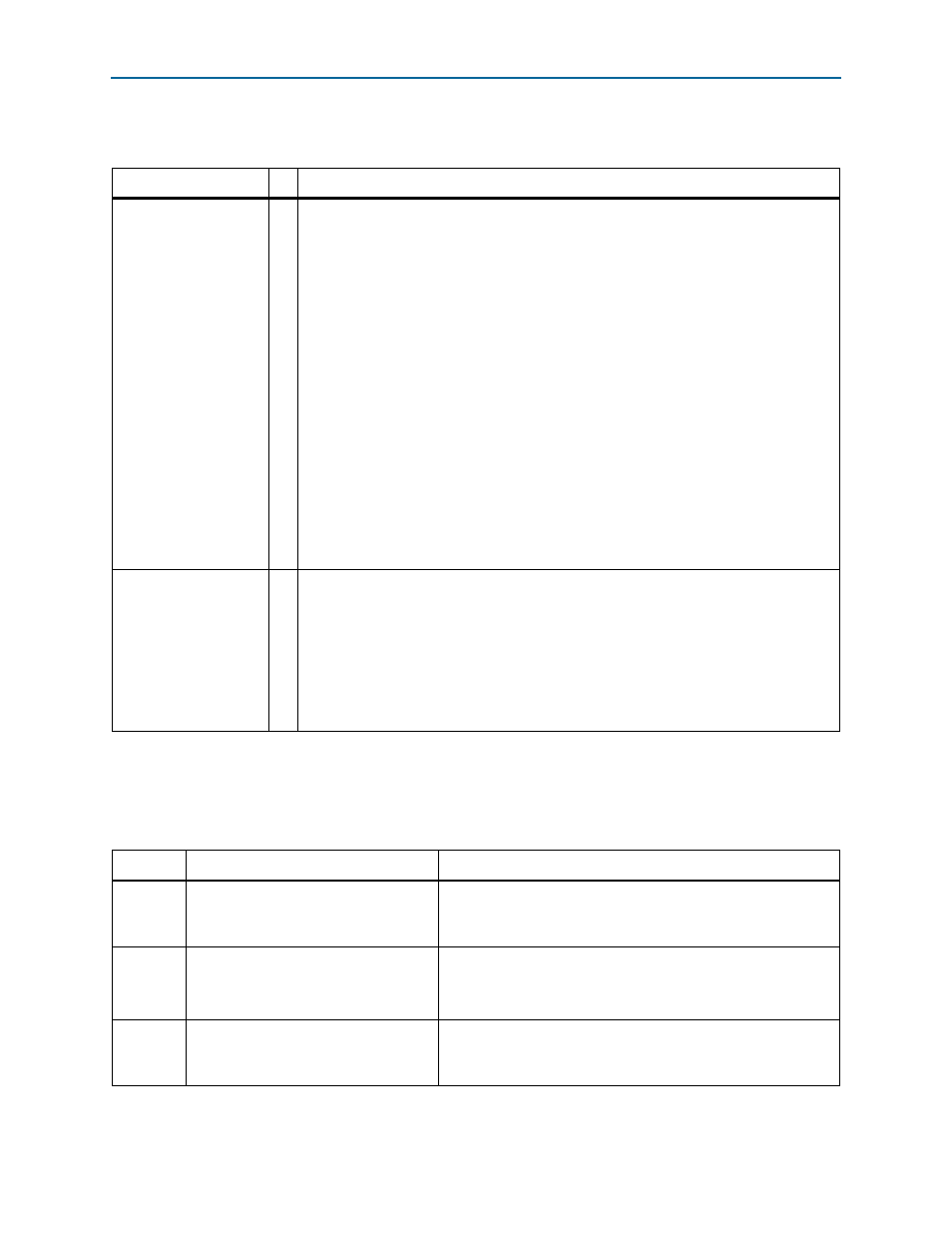

Table B–8. Advanced TX Data Phase Signals

Signal

I/O

Description

tx_cred<n>[65:0]

O

Transmit credit. This signal controls the transmission of transaction layer packets of a

particular type by the application layer based on the number of flow control credits

available. This signal is optional because the IP core always checks for sufficient credits

before acknowledging a request. However, by checking available credits with this signal, the

application can improve system performance by dividing a large transaction layer packet

into smaller transaction layer packets based on available credits or arbitrating among

different types of transaction layer packets by sending a particular transaction layer packet

across a virtual channel that advertises available credits. Each data credit is 4 dwords or 16

bytes as per the PCI Express Base Specification. Refer to

for the bit details.Once

a transaction layer packet is acknowledged by the IP core, the corresponding flow control

credits are consumed and this signal is updated 1 clock cycle after assertion of tx_ack.

For a component that has received infinite credits at initialization, each field of this signal is

set to its highest potential value.

For the ×1 and ×4 IP cores this signal is 22 bits wide with some encoding of the available

credits to facilitate the application layer check of available credits. Refer to

details.

In the ×8 IP core this signal is 66 bits wide and provides the exact number of available

credits for each flow control type. Refer to

for details.

Refer to

for the layout of fields in this signal.

tx_err<n>

I

Transmit error. This signal is used to discard or nullify a transaction layer packet, and is

asserted for one clock cycle during a data phase. The IP core automatically commits the

event to memory and waits for the end of the data phase.

Upon assertion of tx_err, the application interface should stop transaction layer packet

transmission by deasserting tx_dfr and tx_dv.

This signal only applies to transaction layer packets sent to the link (as opposed to

transaction layer packets sent to the configuration space). If unused, this signal can be tied

to zero. This signal is not available in the ×8 IP core.

Note to

(1) For all signals, <n> is the virtual channel number which can be 0 or 1.

Table B–9. tx_cred0[21:0] Bits for the ×1 and ×4 IP cores (Part 1 of 2)

Bits

Value

Description

[0]

■

0: No credits available

■

1: Sufficient credit available for at

least 1 transaction layer packet

Posted header.

[9:1]

■

0: No credits available

■

1-256: number of credits available

■

257-511: reserved

Posted data: 9 bits permit advertisement of 256 credits, which

corresponds to 4 KBytes, the maximum payload size.

[10]

■

0: No credits available

■

1: Sufficient credit available for at

least 1 transaction layer packet

Non-Posted header.