Buffer configuration – Altera IP Compiler for PCI Express User Manual

Page 41

Chapter 3: Parameter Settings

3–5

Parameters in the Qsys Design Flow

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Buffer Configuration

The Buffer Configuration section of the IP Compiler for PCI Express parameter editor

in the Qsys design flow includes parameters for the receive and retry buffers. The IP

Compiler for PCI Express parameter editor also displays the read-only RX buffer

space allocation information.

describes the parameters and information in

this section of the parameter editor in the Qsys design flow.

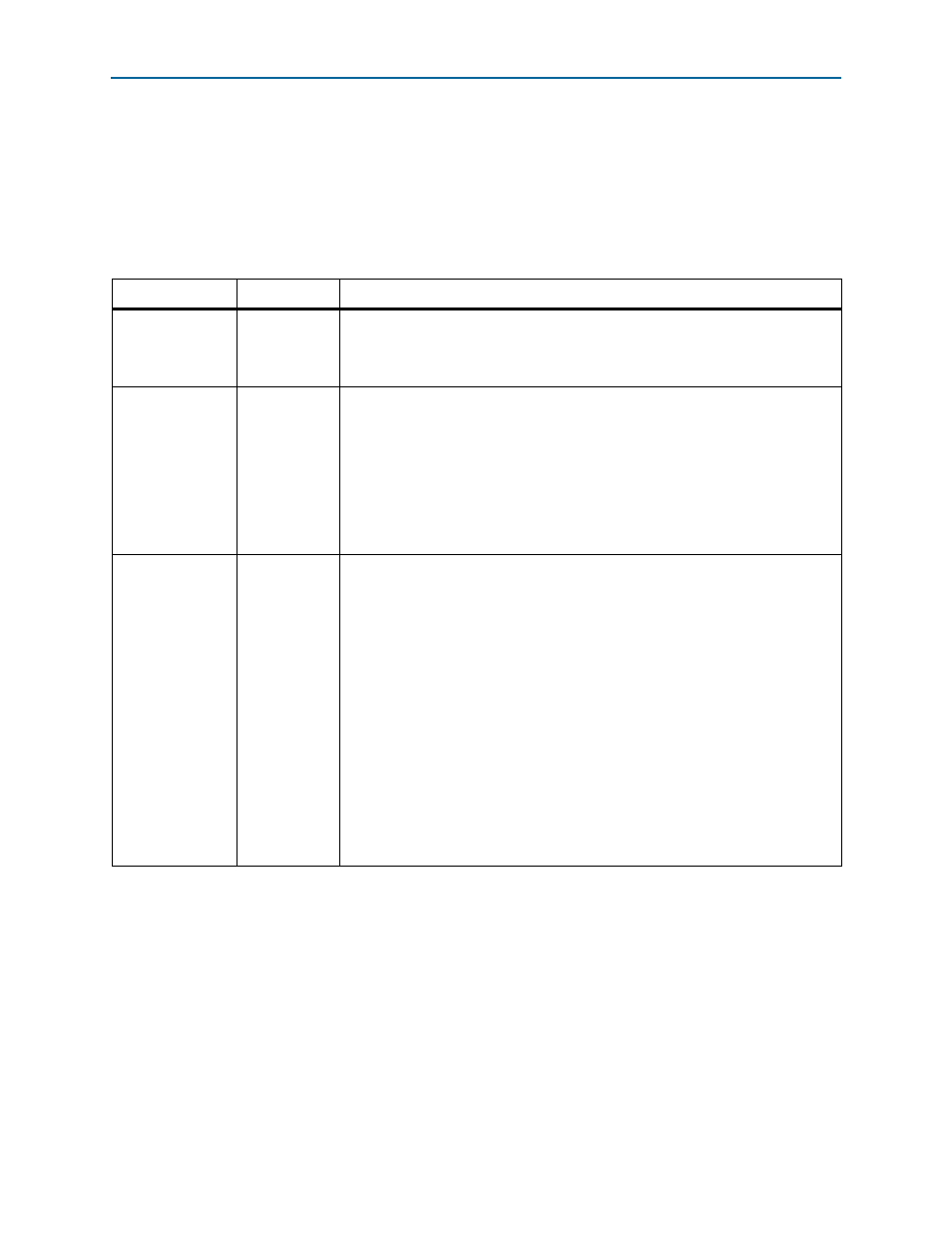

Table 3–6. Buffer Configuration Parameters

Parameter

Value

Description

Maximum

payload size

128 bytes,

256 bytes

Specifies the maximum payload size supported. This parameter sets the read-only

value of the max payload size supported field of the device capabilities register

(0x084[2:0]) and optimizes the IP core for this size payload. Maximum payload size

is 128 bytes or 256 bytes, depending on the device.

RX buffer credit

allocation –

performance for

received requests

Maximum,

High,

Medium, Low

Low—Provides the minimal amount of space for desired traffic. Select this option

when the throughput of the received requests is not critical to the system design.

This setting minimizes the device resource utilization.

Because the Arria II GX and Stratix IV hard IP implementations have a fixed RX

Buffer size, the only available value for these devices is Maximum.

Note that the read-only values for header and data credits update as you change

this setting.

For more information, refer to

Posted header

credit

Posted data credit

Non-posted

header credit

Completion

header credit

Completion data

credit

Read-only

entries

These values show the credits and space allocated for each flow-controllable type,

based on the RX buffer size setting. All virtual channels use the same RX buffer

space allocation.

The entries show header and data credits for RX posted (memory writes) and

completion requests, and header credits for non-posted requests (memory reads).

The table does not show non-posted data credits because the IP core always

advertises infinite non-posted data credits and automatically has room for the

maximum number of dwords of data that can be associated with each non-posted

header.

The numbers shown for completion headers and completion data indicate how much

space is reserved in the RX buffer for completions. However, infinite completion

credits are advertised on the PCI Express link as is required for endpoints. The

application layer must manage the rate of non-posted requests to ensure that the RX

buffer completion space does not overflow. The hard IP RX buffer is fixed at 16

KBytes for Stratix IV GX devices and 4 KBytes for Arria II GX devices.