Test driver module – Altera IP Compiler for PCI Express User Manual

Page 250

15–18

Chapter 15: Testbench and Design Example

Test Driver Module

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

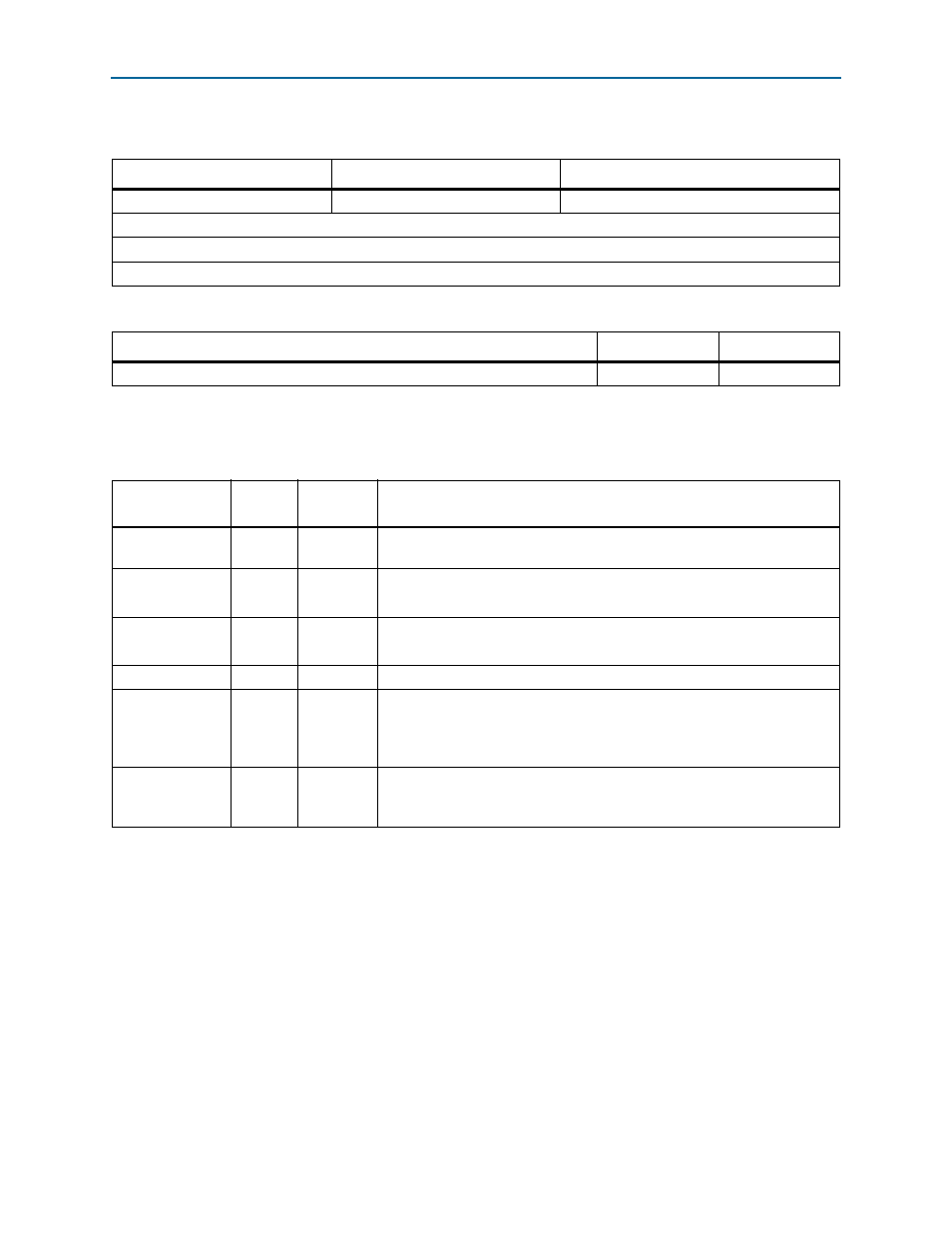

shows the layout of the descriptor fields following the descriptor header.

Each descriptor provides the hardware information on one DMA transfer.

describes each descriptor field.

Test Driver Module

The BFM driver module generated by the parameter editor during the generate step is

configured to test the chaining DMA example endpoint design. The BFM driver

module configures the endpoint configuration space registers and then tests the

example endpoint chaining DMA channel.

For an endpoint VHDL version of this file, see:

<variation_name>_examples/chaining_dma/testbench/

altpcietb_bfm_driver_chaining.vhd

For an endpoint Verilog HDL file, see:

<

variation_name>_examples/chaining_dma/testbench/

altpcietb_bfm_driver_chaining.v

Table 15–11. Chaining DMA Descriptor Format Map

3122

21 16

150

Reserved

Control Fields (refer to

DMA Length

Endpoint Address

RC Address Upper DWORD

RC Address Lower DWORD

Table 15–12. Chaining DMA Descriptor Format Map (Control Fields)

2118

17

16

Reserved

EPLAST_ENA

MSI

Table 15–13. Chaining DMA Descriptor Fields

Descriptor Field

Endpoint

Access

RC Access

Description

Endpoint Address

R

R/W

A 32-bit field that specifies the base address of the memory transfer on the

endpoint site.

RC Address

Upper DWORD

R

R/W

Specifies the upper base address of the memory transfer on the RC site.

RC Address

Lower DWORD

R

R/W

Specifies the lower base address of the memory transfer on the RC site.

DMA Length

R

R/W

Specifies the number of DMA DWORDs to transfer.

EPLAST_ENA

R

R/W

This bit is OR’d with the EPLAST_ENA bit of the control register. When

EPLAST_ENA

is set, the endpoint DMA module updates the EPLAST field of

the descriptor table with the number of the last completed descriptor, in the

form <0 – n>. (Refer to

MSI_ENA

R

R/W

This bit is OR’d with the MSI bit of the descriptor header. When this bit is set

the endpoint DMA module sends an interrupt when the descriptor is

completed.