Altera IP Compiler for PCI Express User Manual

Page 4

1–2

Chapter 1: Datasheet

Features

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

■

Feature rich:

■

Support for ×1, ×2, ×4, and ×8 configurations. You can select the ×2 lane

configuration for the Cyclone

®

IV GX without down configuring a ×4

configuration.

■

Optional end-to-end cyclic redundancy code (ECRC) generation and checking

and advanced error reporting (AER) for high reliability applications.

■

Extensive maximum payload size support:

Stratix IV GX hard IP—Up to 2 KBytes (128, 256, 512, 1,024, or 2,048 bytes).

Arria II GX, Arria II GZ, and Cyclone IV GX hard IP—Up to 256 bytes (128 or

256 bytes).

Soft IP Implementations—Up to 2 KBytes (128, 256, 512, 1,024, or 2,048 bytes).

■

Easy to use:

■

Easy parameterization.

■

Substantial on-chip resource savings and guaranteed timing closure using the

IP Compiler for PCI Express hard IP implementation.

■

Easy adoption with no license requirement for the hard IP implementation.

■

Example designs to get started.

■

Qsys support.

■

Stratix V support is provided by the Stratix V Hard IP for PCI Express.

■

Stratix V support is not available with the IP Compiler for PCI Express.

■

The Stratix V Hard IP for PCI Express is documented in

Different features are available for the soft and hard IP implementations and for the

three possible design flows.

outlines these different features.

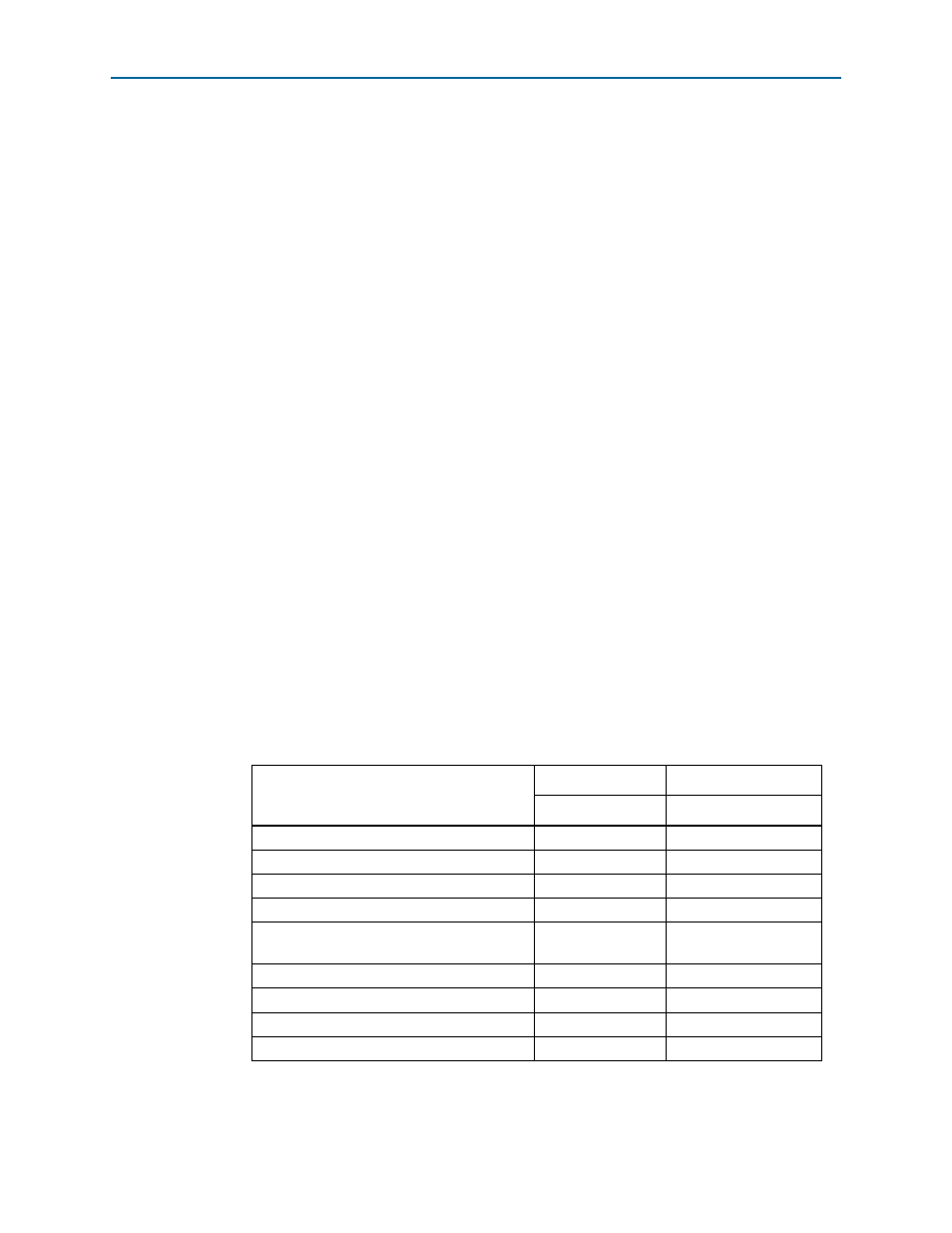

Table 1–2. IP Compiler for PCI Express Features (Part 1 of 2)

Feature

Hard IP

Soft IP

MegaCore License

Free

Required

Root port

Not supported

Not supported

Gen1

×1, ×2, ×4, ×8

×1, ×4

Gen2

×1, ×4

No

Avalon Memory-Mapped (Avalon-MM)

Interface

Supported

Supported

64-bit Avalon Streaming (Avalon-ST) Interface Not supported

Not supported

128-bit Avalon-ST Interface

Not supported

Not supported

Descriptor/Data Interface

Not supported

Not supported

Legacy Endpoint

Not supported

Not supported