Altera IP Compiler for PCI Express User Manual

Page 97

Chapter 5: IP Core Interfaces

5–11

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

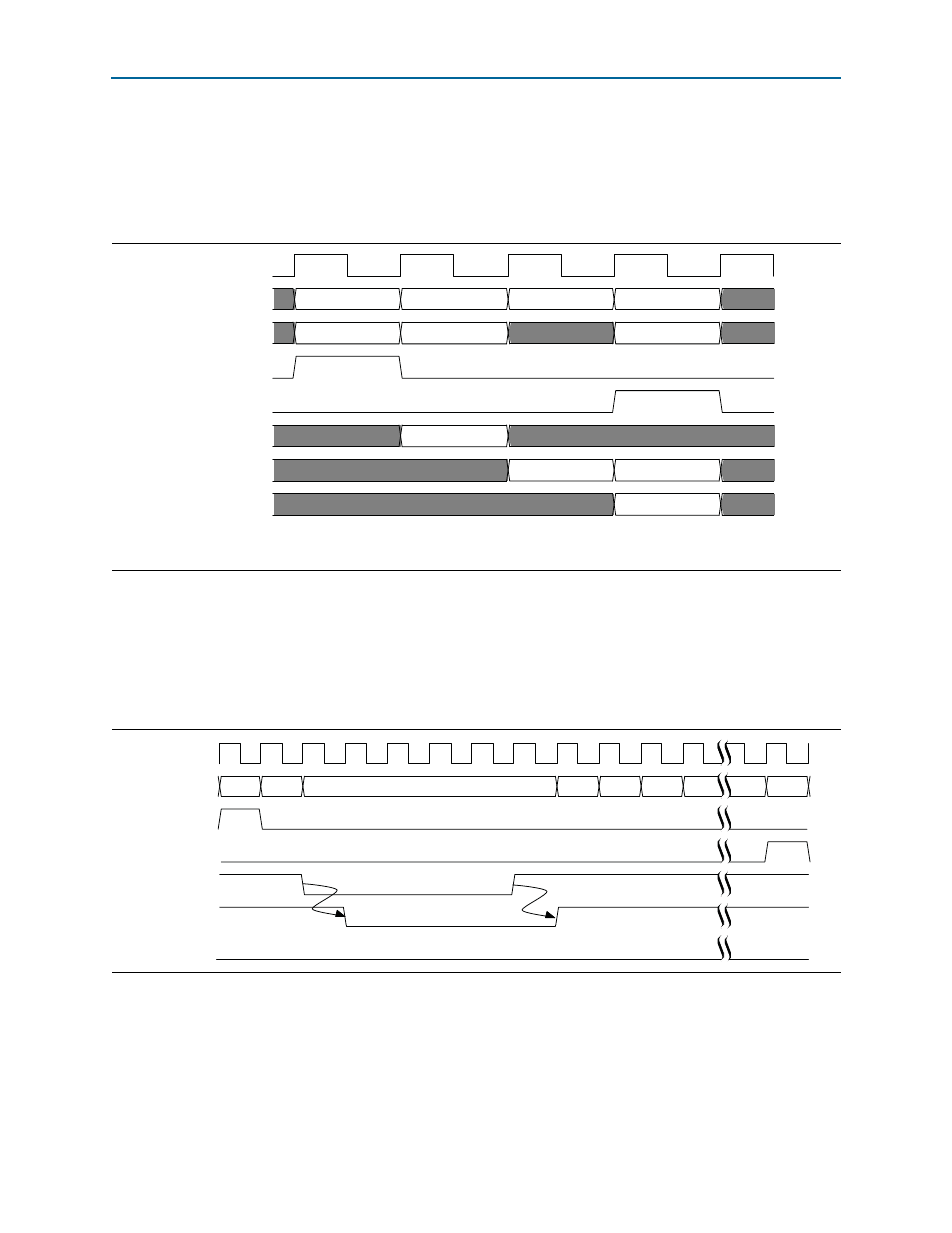

shows the mapping of Avalon-ST RX packet to PCI Express TLPs for TLPs

for a four dword header with non-qword addresses with a 64-bit bus. Note that the

address of the first dword is 0x4. The address of the first enabled byte is 0x6. This

example shows one valid word in the first dword, as indicated by the rx_st_be signal.

illustrates the timing of the RX interface when the application

backpressures the IP Compiler for PCI Express by deasserting rx_st_ready. The

rx_st_valid

signal must deassert within three cycles after rx_st_ready is deasserted.

In this example, rx_st_valid is deasserted in the next cycle. rx_st_data is held until

the application is able to accept it.

Figure 5–8. 64-Bit Avalon-ST rx_st_data<n> Cycle Definitions for 4-DWord Header TLPs with Non-QWord Addresses

Note to

(1) rx_st_be[7:4] corresponds to rx_st_data[63:32]. rx_st_be[3:0] corresponds to rx_st_data[31:0].

clk

rx_st_data[63:32]

rx_st_data[31:0]

rx_st_sop

rx_st_eop

rx_st_bardec[7:0]

rx_st_be[7:4]

rx_st_be[3:0]

header1

header3

data0

data2

header0

header2

data1

10

C

F

F

Figure 5–9. 64-Bit Application Layer Backpressures Transaction Layer

clk

rx_st_data[63:0]

rx_st_sop

rx_st_eop

rx_st_ready

rx_st_valid

rx_st_err

000

. 010

.

CCCC0002CCCC0001

CC

. CC

. CC

. CC

. CC

. CC

.