Or 128-bit avalon-st rx port, Or 128-bit – Altera IP Compiler for PCI Express User Manual

Page 92

5–6

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

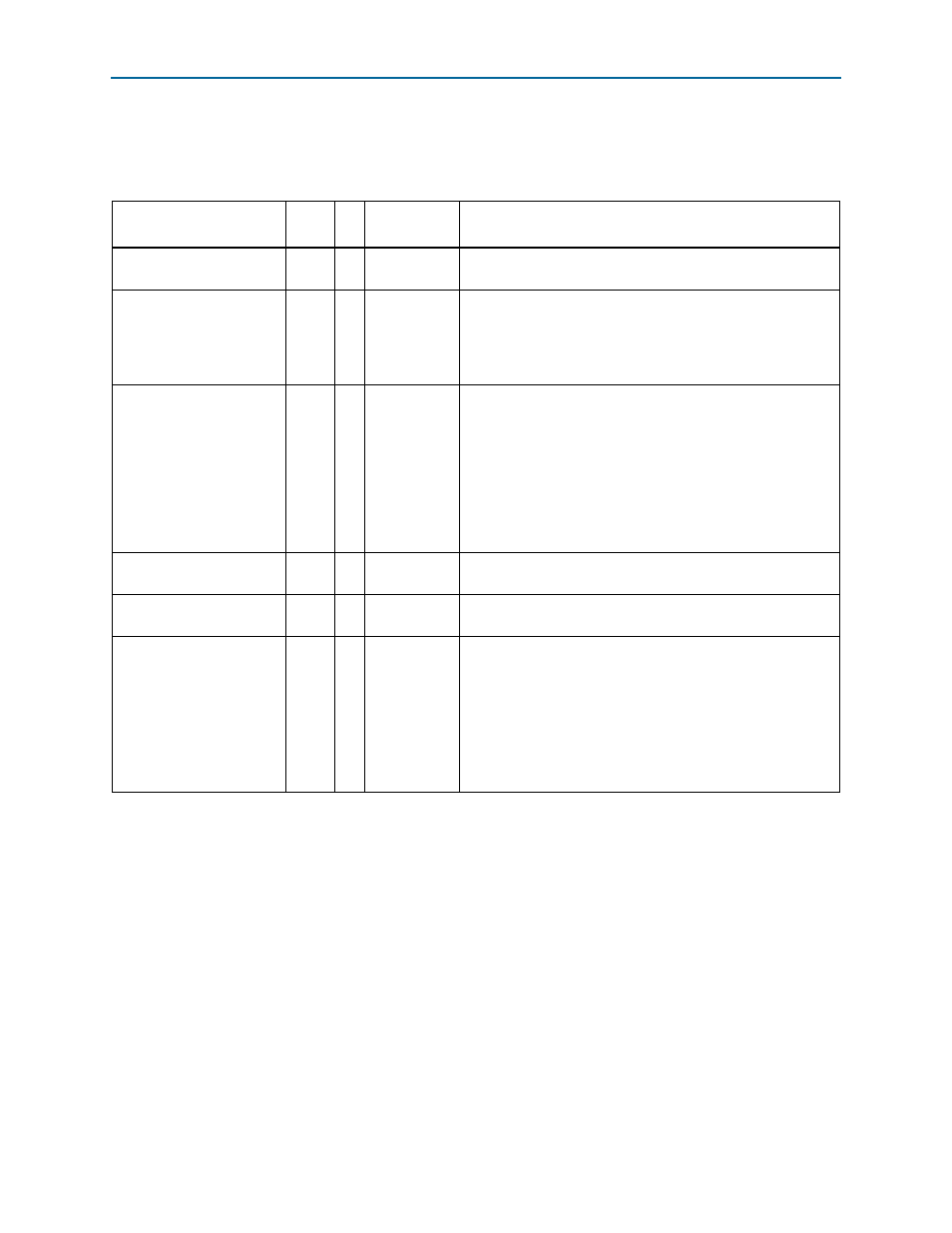

64- or 128-Bit Avalon-ST RX Port

describes the signals that comprise the Avalon-ST RX Datapath.

Table 5–2. 64- or 128-Bit Avalon-ST RX Datapath (Part 1 of 3)

Signal

Width

Dir

Avalon-ST

Type

Description

rx_st_ready

1

I

ready

Indicates that the application is ready to accept data. The

application deasserts this signal to throttle the data stream.

rx_st_valid<n>

1

O

valid

Clocks rx_st_data<n> into application. Deasserts within 3

clocks of rx_st_ready<n> deassertion and reasserts within 3

clocks of rx_st_ready<n> assertion if more data is available

to send. rx_st_valid can be deasserted between the

rx_st_sop

and rx_st_eop even if rx_st_ready is asserted.

rx_st_data<n>

64,

128

O

data

Receive data bus. Refer to

for

the mapping of the transaction layer’s TLP information to

rx_st_data

. Refer to

for the timing. Note that the

position of the first payload dword depends on whether the TLP

address is qword aligned. The mapping of message TLPs is the

same as the mapping of transaction layer TLPs with 4 dword

headers. When using a 64-bit Avalon-ST bus, the width of

rx_st_data<n>

is 64. When using a 128-bit Avalon-ST bus,

the width of rx_st_data<n> is 128.

rx_st_sop<n>

1

O

start of

packet

When asserted with rx_st_valid<n>, indicates that this is the

first cycle of the TLP.

rx_st_eop<n>

1

O

end of

packet

When asserted with rx_st_valid<n>, indicates that this is the

final cycle of the TLP.

rx_st_empty<n>

1 O

empty

Indicates that the TLP ends in the lower 64 bits of rx_st_data.

Valid only when rx_st_eop<n> is asserted. This signal only

applies to 128-bit mode in the hard IP implementation.

When rx_st_eop<n> is asserted and rx_st_empty<n> has

value 1, rx_st_data[63:0] holds valid data but

rx_st_data[127:64]

does not hold valid data.

When rx_st_eop<n> is asserted and rx_st_empty<n> has

value 0, rx_st_data[127:0] holds valid data.