Table b–2 – Altera IP Compiler for PCI Express User Manual

Page 322

B–4

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

describes the standard RX descriptor phase signals.

Table B–2. RX Descriptor Phase Signals (Part 1 of 2)

Signal

I/O

Description

rx_req<n>

O

Receive request. This signal is asserted by the IP core to request a packet transfer to the

application interface. It is asserted when the first 2 DWORDS of a transaction layer

packet header are valid. This signal is asserted for a minimum of 2 clock cycles;

rx_abort

, rx_retry, and rx_ack cannot be asserted at the same time as this signal.

The complete descriptor is valid on the second clock cycle that this signal is asserted.

rx_desc<n>[135:0]

O

Receive descriptor bus. Bits [125:0] have the same meaning as a standard transaction

layer packet header as defined by the

. Byte 0 of the header occupies bits [127:120] of the rx_desc bus, byte 1 of the

header occupies bits [119:112], and so on, with byte 15 in bits [7:0]. Refer to

Appendix A, Transaction Layer Packet (TLP) Header Formats

for the header formats.

For bits [135:128] (descriptor and BAR decoding), refer to

. Completion

transactions received by an endpoint do not have any bits asserted and must be routed

to the master block in the application layer.

rx_desc[127:64]

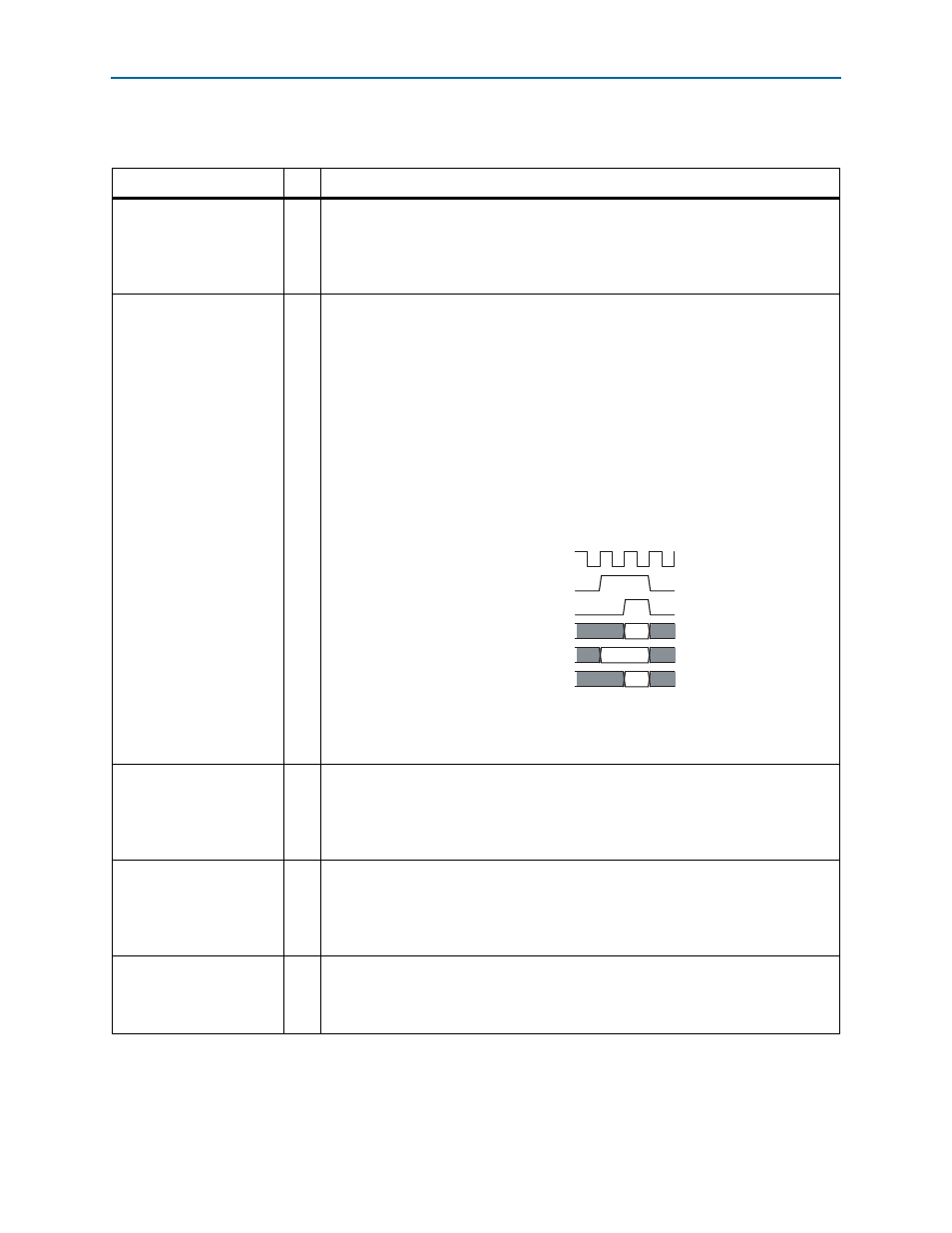

begins transmission on the same clock cycle that rx_req is

asserted, allowing precoding and arbitration to begin as quickly as possible. The other

bits of rx_desc are not valid until the following clock cycle as shown in the following

figure.

Bit 126 of the descriptor indicates the type of transaction layer packet in transit:

■

rx_desc[126]

when set to 0: transaction layer packet without data

■

rx_desc[126]

when set to 1: transaction layer packet with data

rx_ack<n>

I

Receive acknowledge. This signal is asserted for 1 clock cycle when the application

interface acknowledges the descriptor phase and starts the data phase, if any. The

rx_req

signal is deasserted on the following clock cycle and the rx_desc is ready for

the next transmission. rx_ack is independent of rx_dv and rx_data. It cannot be

used to backpressure rx_data. You can use rx_ws to insert wait states.

rx_abort<n>

I

Receive abort. This signal is asserted by the application interface if the application

cannot accept the requested descriptor. In this case, the descriptor is removed from the

receive buffer space, flow control credits are updated, and, if necessary, the application

layer generates a completion transaction with unsupported request (UR) status on the

transmit side.

rx_retry

<n>

I

Receive retry. The application interface asserts this signal if it is not able to accept a

non-posted request. In this case, the application layer must assert rx_mask<n> along

with rx_retry<n> so that only posted and completion transactions are presented on

the receive interface for the duration of rx_mask<n>.

clk

rx_req

rx_ack

rx_desc[135:128]

rx_desc[127:64]

rx_desc[63:0]

valid

valid

valid

1

2

3

4