Selecting an external phy – Altera IP Compiler for PCI Express User Manual

Page 230

14–10

Chapter 14: External PHYs

Selecting an External PHY

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Selecting an External PHY

You can select an external PHY and set the appropriate options in the parameter

editor.

■

Select the specific PHY.

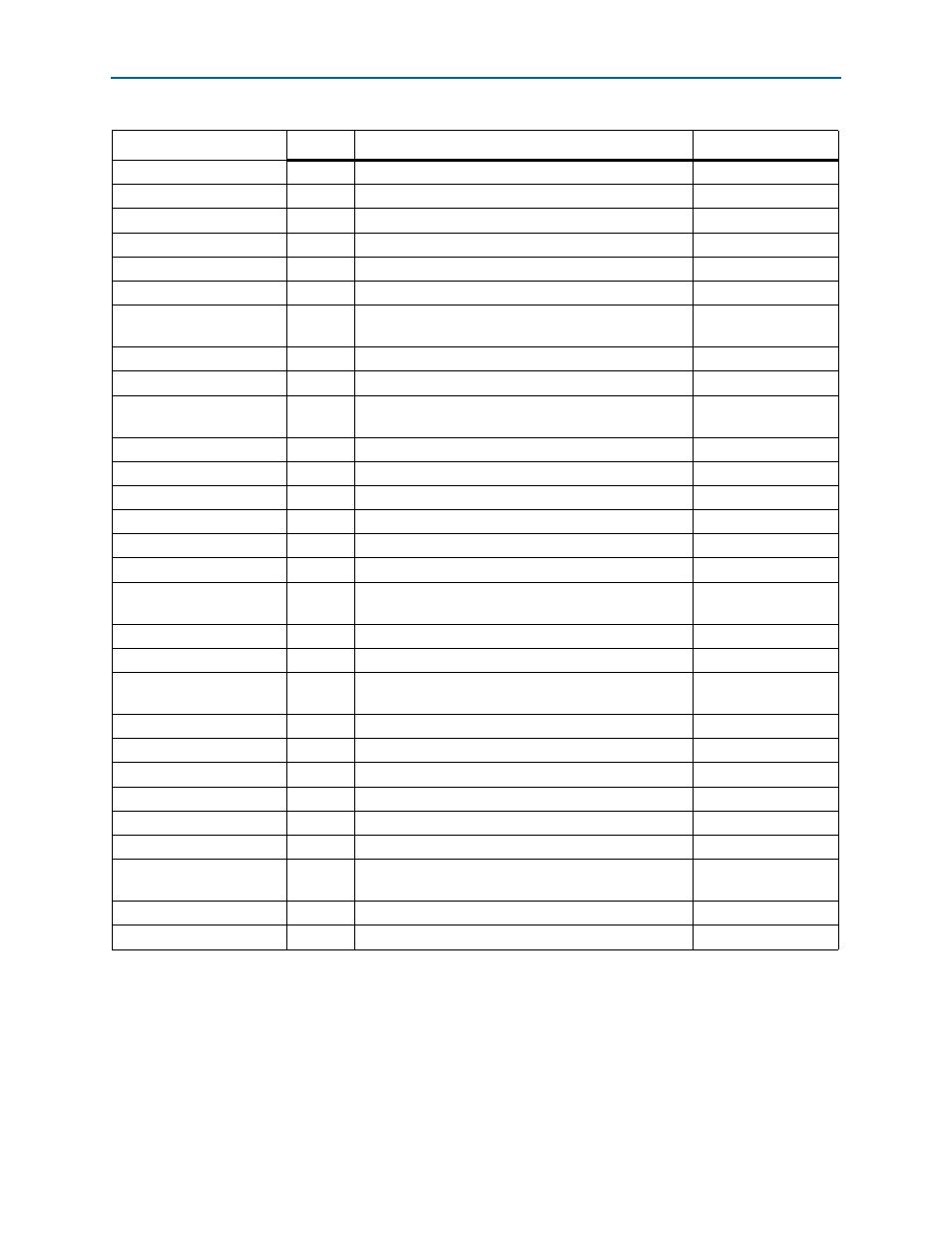

rxdatak1_ext

I

Pipe interface lane 1 RX data K-character flag.

Only in ×4

rxelecidle1_ext

I

Pipe interface lane 1 RX electrical idle indication.

Only in ×4

rxpolarity1_ext

O

Pipe interface lane 1 RX polarity inversion control.

Only in ×4

rxstatus1_ext[1:0]

I

Pipe interface lane 1 RX status flags.

Only in ×4

rxvalid1_ext

I

Pipe interface lane 1 RX valid indication.

Only in ×4

txcompl1_ext

O

Pipe interface lane 1 TX compliance control.

Only in ×4

txdata1_ext[7:0]

O

Pipe interface lane 1 TX data signals, carries the parallel

transmit data.

Only in ×4

txdatak1_ext

O

Pipe interface lane 1 TX data K-character flag.

Only in ×4

txelecidle1_ext

O

Pipe interface lane 1 TX electrical idle control.

Only in ×4

rxdata2_ext[7:0]

I

Pipe interface lane 2 RX data signals, carries the parallel

received data.

Only in ×4

rxdatak2_ext

I

Pipe interface lane 2 RX data K-character flag.

Only in ×4

rxelecidle2_ext

I

Pipe interface lane 2 RX electrical idle indication.

Only in ×4

rxpolarity2_ext

O

Pipe interface lane 2 RX polarity inversion control.

Only in ×4

rxstatus2_ext[1:0]

I

Pipe interface lane 2 RX status flags.

Only in ×4

rxvalid2_ext

I

Pipe interface lane 2 RX valid indication.

Only in ×4

txcompl2_ext

O

Pipe interface lane 2 TX compliance control.

Only in ×4

txdata2_ext[7:0]

O

Pipe interface lane 2 TX data signals, carries the parallel

transmit data.

Only in ×4

txdatak2_ext

O

Pipe interface lane 2 TX data K-character flag.

Only in ×4

txelecidle2_ext

O

Pipe interface lane 2 TX electrical idle control.

Only in ×4

rxdata3_ext[7:0]

I

Pipe interface lane 3 RX data signals, carries the parallel

received data.

Only in ×4

rxdatak3_ext

I

Pipe interface lane 3 RX data K-character flag.

Only in ×4

rxelecidle3_ext

I

Pipe interface lane 3 RX electrical idle indication.

Only in ×4

rxpolarity3_ext

O

Pipe interface lane 3 RX polarity inversion control.

Only in ×4

rxstatus3_ext[1:0]

I

Pipe interface lane 3 RX status flags.

Only in ×4

rxvalid3_ext

I

Pipe interface lane 3 RX valid indication.

Only in ×4

txcompl3_ext

O

Pipe interface lane 3 TX compliance control.

Only in ×4

txdata3_ext[7:0]

O

Pipe interface lane 3 TX data signals, carries the parallel

transmit data.

Only in ×4

txdatak3_ext

O

Pipe interface lane 3 TX data K-character flag.

Only in ×4

txelecidle3_ext

O

Pipe interface lane 3 TX electrical idle control.

Only in ×4

Table 14–3. 8-bit PHY Interface Signals (Part 2 of 2)

Signal Name

Direction

Description

Availability