Support for ip compiler for pci express hard ip – Altera IP Compiler for PCI Express User Manual

Page 7

Chapter 1: Datasheet

1–5

General Description

August 2014

Altera Corporation

The hard IP implementation includes all of the required and most of the optional

features of the specification for the transaction, data link, and physical layers.

Depending upon the device you choose, one to four instances of the IP Compiler for

PCI Express hard implementation are available. These instances can be configured to

include any combination of root port and endpoint designs to meet your system

requirements. A single device can also use instances of both the soft and hard

implementations of the IP Compiler for PCI Express.

provides a high-level

block diagram of the hard IP implementation.

This user guide includes a design example and testbench that you can configure as a

root port (RP) or endpoint (EP). You can use these design examples as a starting point

to create and test your own root port and endpoint designs.

f

The purpose of the IP Compiler for PCI Express User Guide is to explain how to use the

IP Compiler for PCI Express and not to explain the PCI Express protocol. Although

there is inevitable overlap between the two documents, this document should be used

in conjunction with an understanding of the following PCI Express specifications:

and

.

Support for IP Compiler for PCI Express Hard IP

If you target an Arria II GX, Arria II GZ, Cyclone IV GX, or Stratix IV GX device, you

can parameterize the IP core to include a full hard IP implementation of the PCI

Express stack including the following layers:

■

Physical (PHY)

■

Physical Media Attachment (PMA)

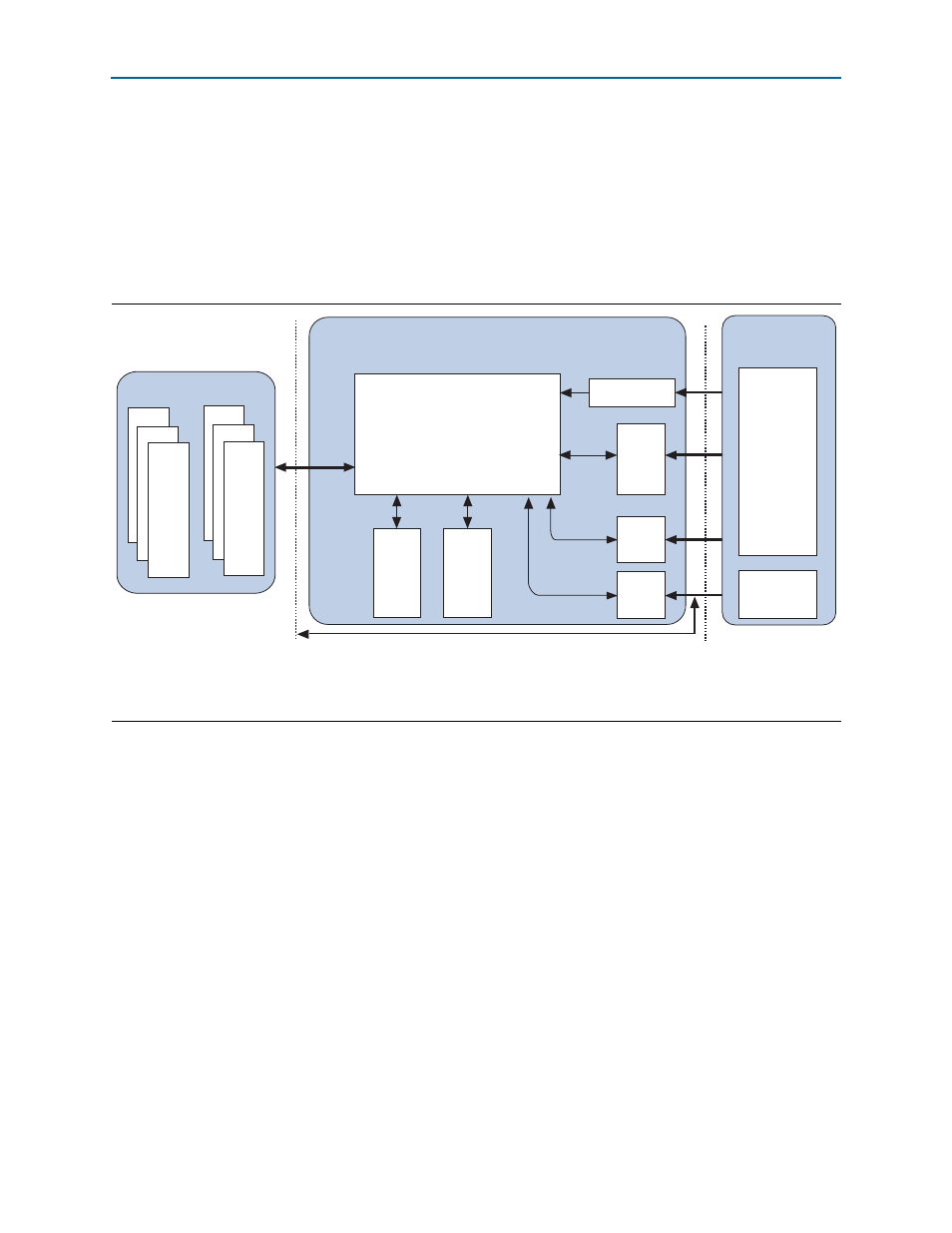

Figure 1–1. IP Compiler for PCI Express Hard IP Implementation High-Level Block Diagram

Notes to

(1) Stratix IV GX devices have two virtual channels.

(2) LMI stands for Local Management Interface.

PCI Express

Protocol Stack

Adapter

Clock & Reset

Selection

PCIe Hard IP Block

TL

Interface

FPGA Fabric Interface

PIPE Interface

LMI

PCIe

Reconfig

Buffer

Virtual

Channel

Buffer

Retry

PCIe Hard IP Block Reconfiguration

RX

FPGA Fabric

Application

Layer

Test, Debug &

Configuration

Logic

PMA

PCS

Transceivers