Altera IP Compiler for PCI Express User Manual

Page 332

B–14

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

tx_data

<n>[63:0]

I

Transmit data bus. This signal transfers data from the application interface to the link. It is

2 DWORDS wide and is naturally aligned with the address in one of two ways, depending

on bit 2 of the transaction layer packet address, which is located on bit 2 or 34 of the

tx_desc

(depending on the 3 or 4 DWORDS transaction layer packet header bit 125 of the

tx_desc

signal).

■

tx_desc[2]

(64-bit address) when 0: The first DWORD is located on tx_data[31:0].

■

tx_desc[34]

(32-bit address) when 0: The first DWORD is located on bits

tx_data[31:0]

.

■

tx_desc[2]

(64-bit address) when 1: The first DWORD is located on bits

tx_data[63:32]

.

■

tx_desc[34]

(32-bit address) when 1: The first DWORD is located on bits

tx_data[63:32]

.

This natural alignment allows you to connect the tx_data[63:0] directly to a 64-bit

datapath aligned on a QWORD address (in the little endian convention).

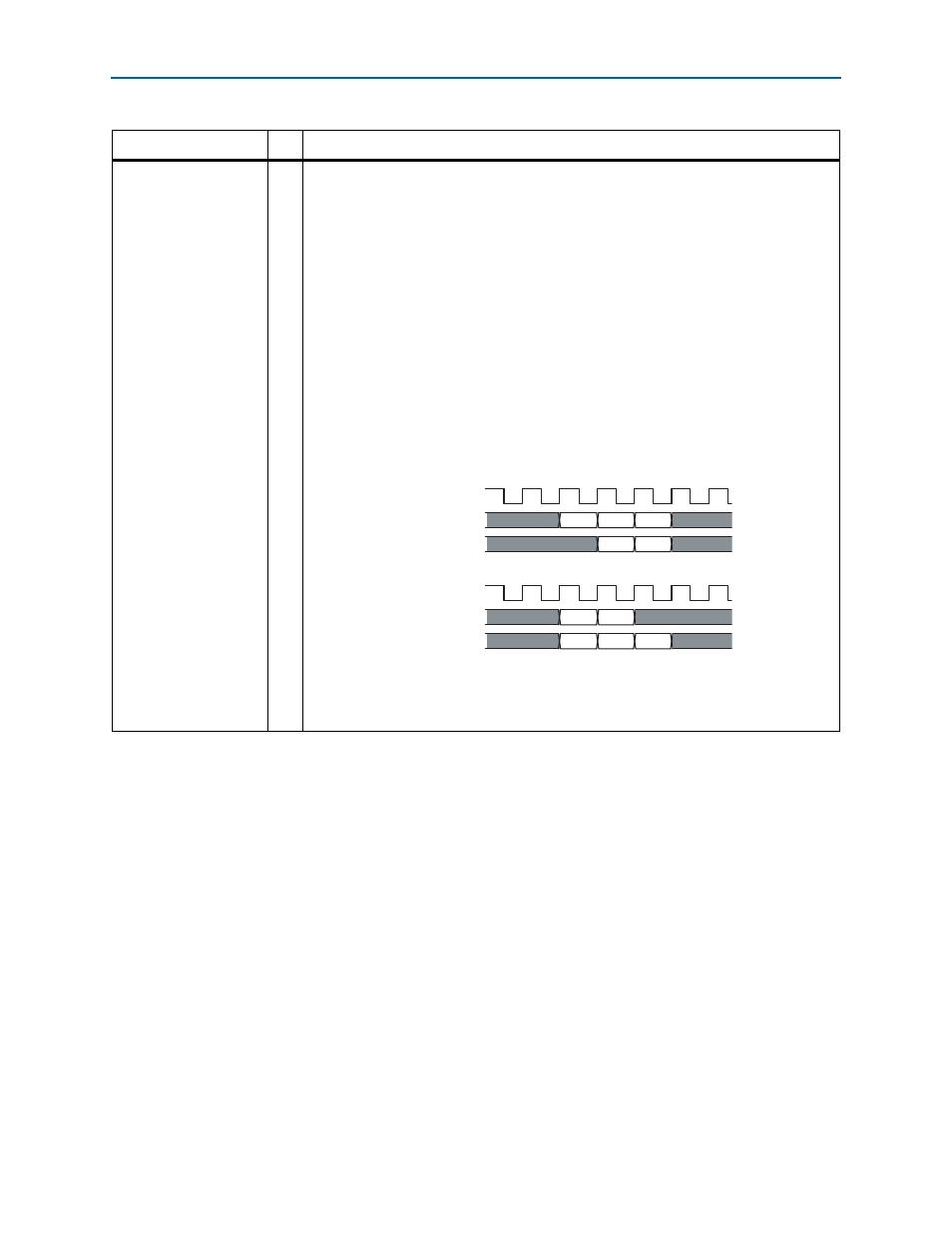

Figure B–10. Bit 2 is set to 1 (5 DWORDS transaction)

Figure B–11. Bit 2 is set to 0 (5 DWORDS transaction)

The application layer must provide a properly formatted TLP on the TX Data interface. The

number of data cycles must be correct for the length and address fields in the header.

Issuing a packet with an incorrect number data cycles will result in the TX interface

hanging and unable to accept further requests.

Note to

(1) For all signals, <n> is the virtual channel number which can be 0 or 1.

Table B–7. Standard TX Data Phase Signals (Part 2 of 2)

Signal

I/O

Description

clk

tx_data[63:32]

tx_data[31:0]

DW 0

DW 2

DW 4

DW 1

DW 3

1

2

3

4

5

6

7

clk

tx_data[63:32]

tx_data[31:0]

DW 1

DW 3

DW 0

DW 2

DW 4

1

2

3

4

5

6

7