Altera JNEye User Manual

Page 15

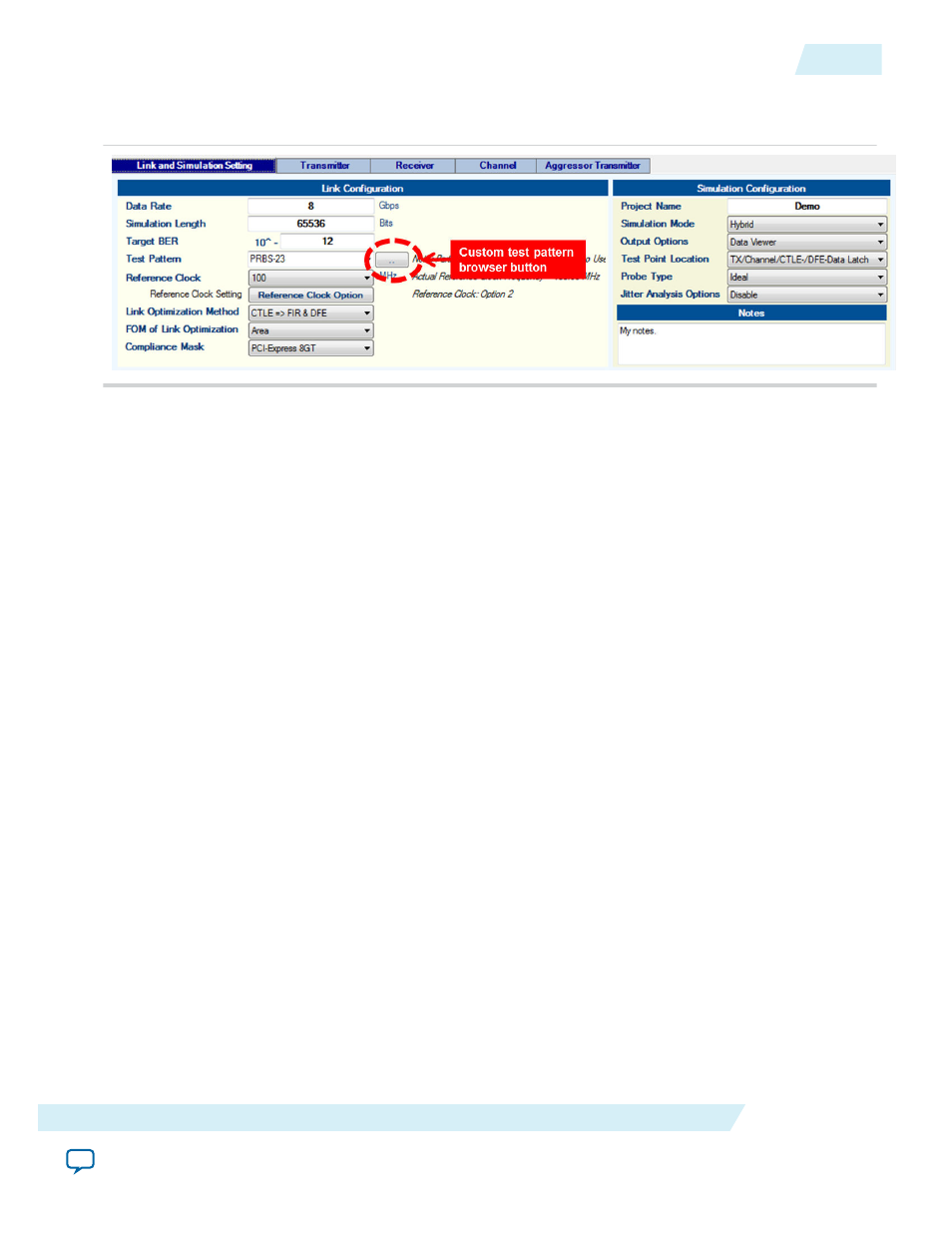

• Custom—Click the open-file dialog button to select a custom test pattern file.

Figure 2-7: Custom Test Pattern File Browser Button

The custom pattern files are in the following formats:

• Hexadecimal—Hexadecimal strings start with

0x

. For example, a PRBS-7 test pattern can be

specified by 0x8cd501fbe7ae1ba62b05e3b64a4272d0. The custom file name must have a

.hex

extension.

• Binary—Binary strings have a format such as "001000111…". Blank characters and new lines/

returns are allowed in the input binary string file. The custom file name must have a

.bin

extension.

Note: The custom test pattern has a maximum text length of 262,142 characters (about 1M bits with a

hexadecimal text format or about 246K bits with a binary text format). Altera recommends that

the test pattern string (hexadecimal or binary) is specified in a single row without spaces,

especially for long custom test patterns. If a custom test pattern is input with multiple lines of

text, the line returns or end-of-line control characters on each line of text are counted as an item

or entry by the text parser.

Reference Clock

Specifies the reference clock that feeds into the transmitter. The supported clock frequencies are shown in

MHz. By default, the reference is assumed to be ideal without any noise or jitter. You can configure and

specify the reference clock characteristics by clicking Reference Clock Option.

The reference clock can be fed to a transmitter with or without enabling a phase-locked loop (PLL)

module. When the transmitter PLL is disabled or not present, the reference clock noise and jitter directly

affects the serial output signal.

With integer PLLs, JNEye supports an integer divider ratio between the data rate and the reference clock

frequency. If the ratio is not an integer, the reference clock frequency is rounded to the closest integer-

divided-ratio frequency. The actual reference clock frequency used in the simulation is displayed in the

message box next to the pull-down menu. With fractional-N PLLs, fractional divider ratios are allowed.

In the simulation with specific transmitter devices, such as Arria 10 GX/SX/GT, Stratix V GT, Stratix V

GX, and Arria V GZ devices, the supported data rate to reference clock divider ratios are limited. If a

specific combination of data rate, PLL divider ratio, and reference clock frequency cannot be found, the

reference clock used in the simulation can be further adjusted.

UG-1146

2015.05.04

Link and Simulation Setting

2-9

Functional Description

Altera Corporation