Altera JNEye User Manual

Page 166

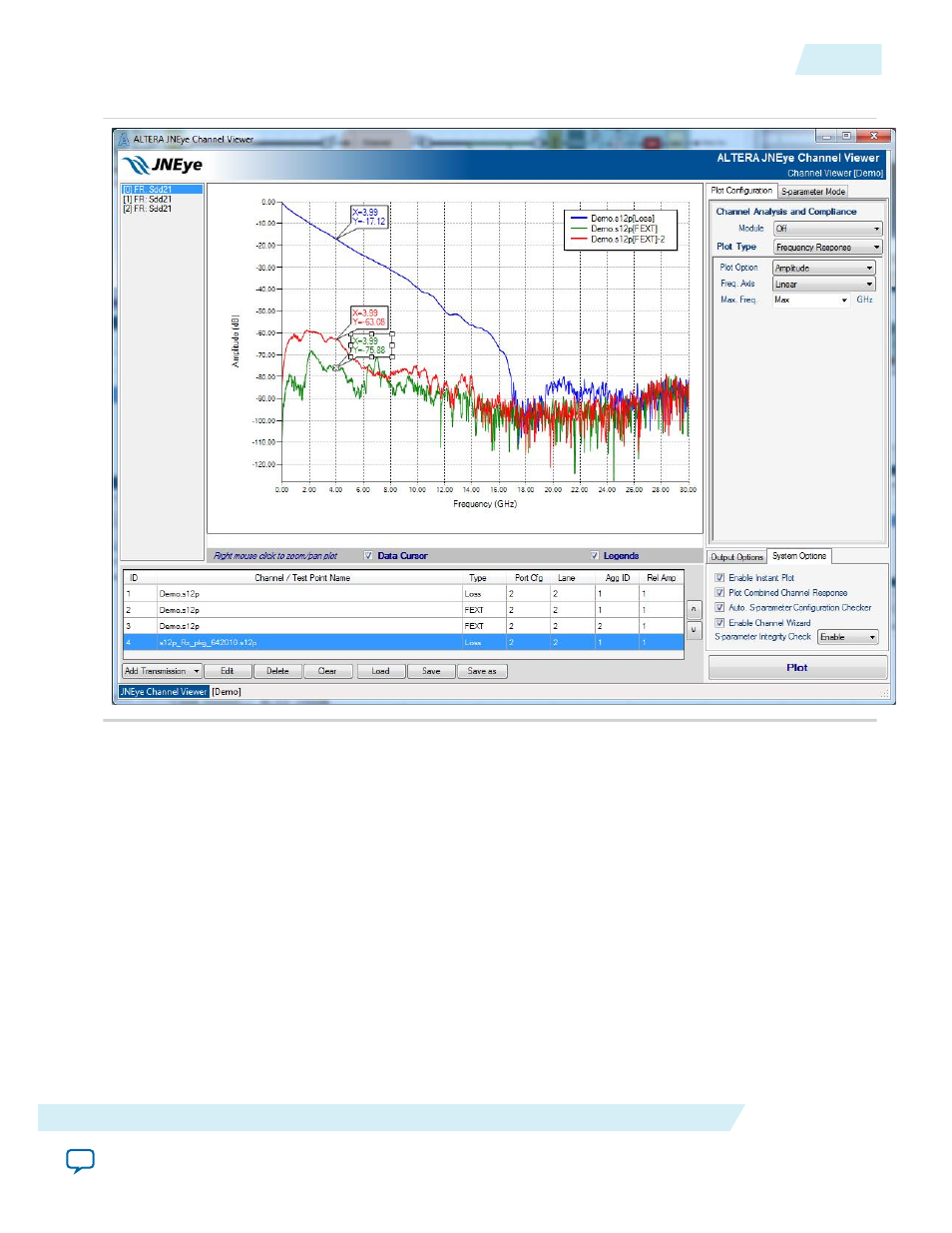

Figure 3-14: Channel Characteristics of Victim and 2 FEXT Channels (with Data Cursor Enabled)

Start the channel simulation by clicking Simulate in the lower right corner of the JNEye Control Module.

The JNEye Simulation Engine simulates all the models and generates eye diagrams at test points and

inside the receiver (after CTLE and DFE).

A goal of this tutorial was for JNEye to automatically find the optimal link setting for both transmitter and

receiver. In the simulation time, the progress bar flashes, indicating the JNEye Simulation Engine is

exploring the solution space. The link performance and result of the final setting is shown in a JNEye Data

View.

At TX output, which is located after the Altera Stratix V GX transmitter output pin (after the TX package

model), the results are shown in the following figure. JNEye found the optimal TX-FIR setting: Pre-tap 1

= –4, Post-tap 1 = 2, and Post-tap 2 = 0. The configured transmitter generates ~0.83 UI of jitter at BER =

10

-12

. This set of TX outputs is measured with an ideal clock. In addition to the transmitter’s intrinsic

jitter, the reference clock’s jitter and noise (recall that external reference clock phase noise and spurs in

this simulation are filtered by the Stratix V GX ’s PLL) are seen here.

UG-1146

2015.05.04

Analysis

3-15

Tutorial: PCI Express 8GT

Altera Corporation