Altera JNEye User Manual

Page 170

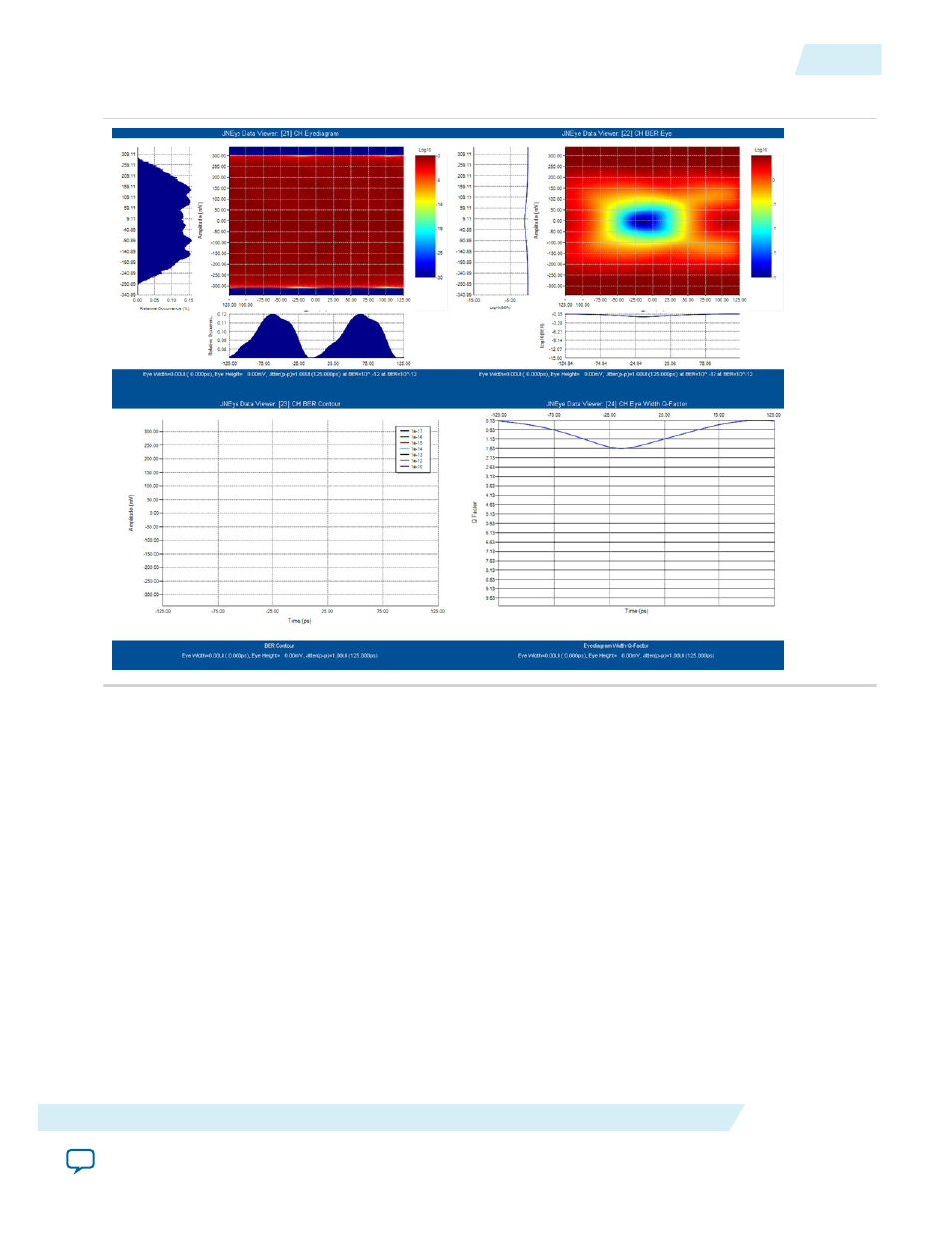

Figure 3-19: Channel Output Hybrid Eye Diagrams and BER Analysis

The CTLE is a PCI-Express 8GT CTLE behavior model output stage. The JNEye's link optimization

algorithm has identified the optimal gain setting at 10 dB level. Similar to the TX output case, when the

receiver CDR is enabled or included in the simulation, two sets of CTLE outputs are shown. The first set

of outputs is with the ideal clock and the second one is with the CDR recovered clock. The total jitter is 1

UI (at BER < 10

-12

, with ideal clock) or 0.54 UI (with CDR recovered clock). The eye diagram opening

height is 0 mV (with ideal clock) and 41 mV (with recovered clock). The eye diagram opening is marginal

to PCI-Express 8GT requirements. Therefore, further equalization of the signal with DFE is needed.

UG-1146

2015.05.04

Analysis

3-19

Tutorial: PCI Express 8GT

Altera Corporation