Ip core verification, Simulation environment, Compatibility testing environment – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 10: Performance and resource utilization, Ip core verification –4, Performance and resource utilization –4

1–4

Chapter 1: About This IP Core

IP Core Verification

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

1.4. IP Core Verification

To ensure compliance with the IEEE specification, Altera performs extensive

validation of the 10GbE MAC IP core. Validation includes both simulation and

hardware testing.

1.4.1. Simulation Environment

Altera performs the following tests in the simulation environment:

■

Directed tests that test all types and sizes of transaction layer packets and all bits of

the configuration space.

■

Error injection tests that inject errors in the link, transaction layer packets, and data

link layer packets, and check for the proper response from the IP core.

■

Random tests that test a wide range of traffic patterns across one or more virtual

channels.

1.4.2. Compatibility Testing Environment

Altera has performed significant hardware testing of the 10GbE MAC IP core to

ensure a reliable solution. The IP core has been tested with the following devices:

■

Arria V, Stratix IV, and Stratix V

■

Soft XAUI PHY

■

Soft and hard 10GBASE-R PHY

■

Hard Backplane Ethernet 10GBASE-KR PHY

■

1G/10Gbps Ethernet PHY

The IP core has passed all interoperability tests conducted by the UNH. In addition,

Altera internally tests every release with the Spirent Ethernet and 10G testers.

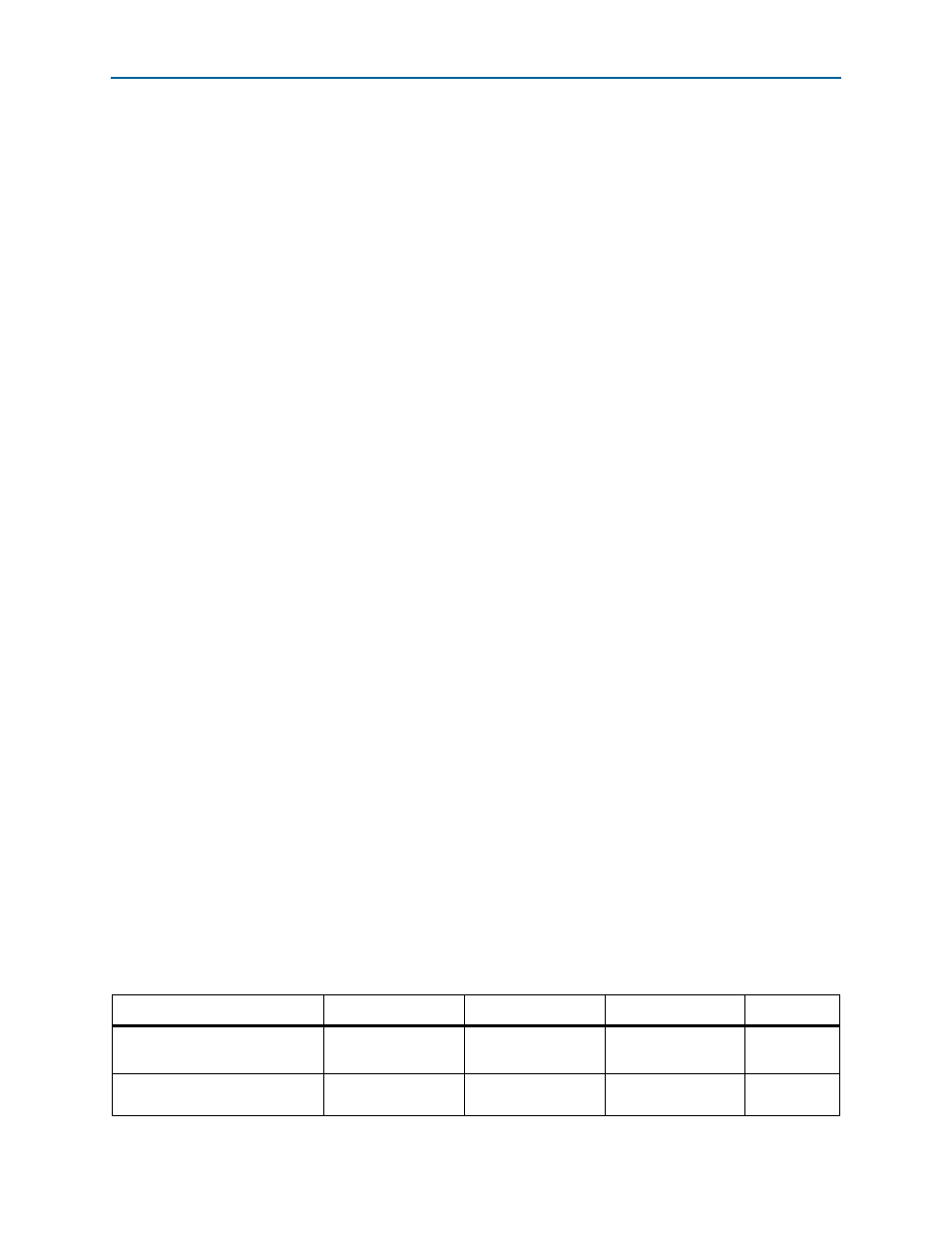

1.5. Performance and Resource Utilization

Table 1–4

provides the estimated performance and resource utilization of the 10GbE

MAC for the Cyclone IV device family. The estimates are obtained by compiling the

10GbE MAC with the Quartus II software targeting a Cyclone IV

(EP4CGX110DF31C7) device with speed grade –7.

1

To achieve your timing requirement in the Quartus II software, Altera recommends

that you use multiple seeds in the Design Space Explorer to find the optimal Fitter

settings for your design, follow the recommendations of the Timing Optimization

Advisor, apply the Speed Optimization Technique and use the LogicLock regions.

Table 1–4. Cyclone IV Performance and Resource Utilization

Settings

Logic Elements

Logic Registers

Memory Block (M9K)

f

MAX

(MHz)

All options disabled

4,424

3,245

2

>156.25

All options enabled with

memory-based statistics counters

11,845

8,355

11

>156.25