10gbe design example parameter settings, 10gbe testbenches, 10gbe testbench – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 26: 10gbe testbench –8

3–8

Chapter 3: 10GbE MAC Design Examples

10GbE Design Example Parameter Settings

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

3.5. 10GbE Design Example Parameter Settings

You can customize the 10GbE design example by specifying the parameters using the

parameter editor.

Table 3–4

describes these parameters.

1

The parameter values you select on Configuration tab correspond with the

other tabs that require further parameterization. You should only

parameterize the components you selected and omit the others. Editing the

component parameters that were not selected may cause the system

generation to fail.

f

For more information about the parameter settings of other components,

refer to the respective documents:

■

10GbE MAC, refer to

“10GbE MAC Parameter Settings” on page 2–6

■

Avalon-ST Single-Clock or Dual-Clock FIFO and MDIO core, refer to

■

XAUI PHY and 10GBASE-R PHY, re

3.6. 10GbE Testbenches

Altera provides testbenches for you to verify the design examples. The following

sections in this document describe the testbench, its components, and use.

3.6.1. 10GbE Testbench

The testbenches operate in loopback mode.

shows the flow of the packets.

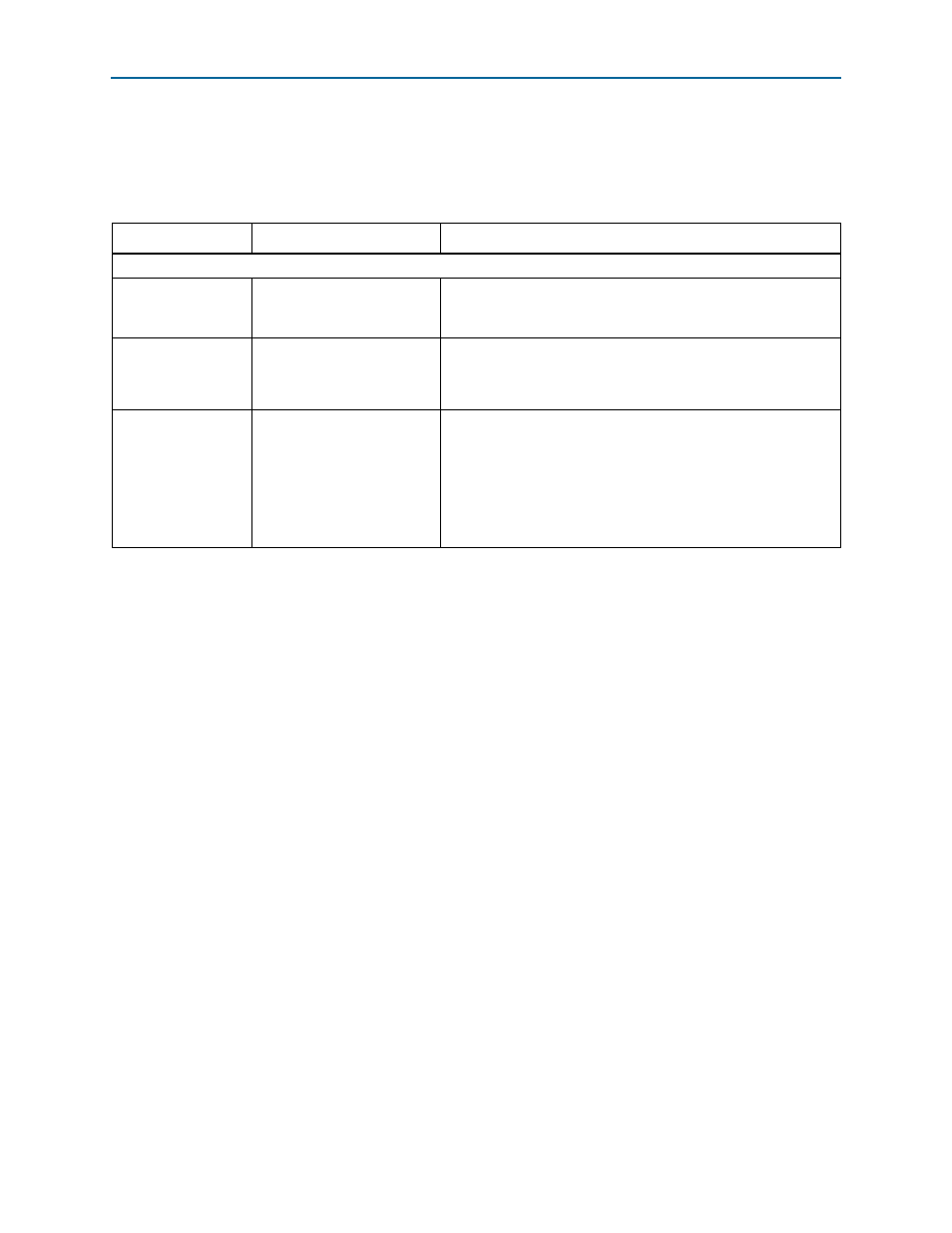

Table 3–4. Design Example Parameters

Name

Value

Description

Configuration

MDIO

MDIO

None

Specifies whether the Ethernet system requires a MDIO core to

access the external PHY device management registers for

configuration and management purposes.

PHY IP

XAUI PHY

10GBase-R PHY

None

Specifies which protocol-specific PHY IP core to use for the

Ethernet system. For XAUI PHY, you can choose to implement the

system in soft or hard logic.

FIFO

Avalon-ST Single Clock FIFO

Avalon-ST Dual Clock FIFO

Avalon-ST Single Clock FIFO

+ Avalon-ST Dual Clock FIFO

None

Specifies which FIFO buffer to use for the Ethernet system. The

Avalon-ST Single Clock FIFO operates with a common clock for the

input and output ports while the Avalon-ST Dual Clock FIFO

operates with independent clocks for the input and output ports.

You cannot enable a different FIFO option for TX datapath and RX

datapath. If you select Avalon-ST Single Clock FIFO, the design

includes single clock FIFO at both TX and RX datapaths.