Timing diagrams—sdr xgmii, Timing diagrams—sdr xgmii –9, Figure 9–7. sdr xgmii rx interface data bus – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 128

Chapter 9: Interface Signals

9–9

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

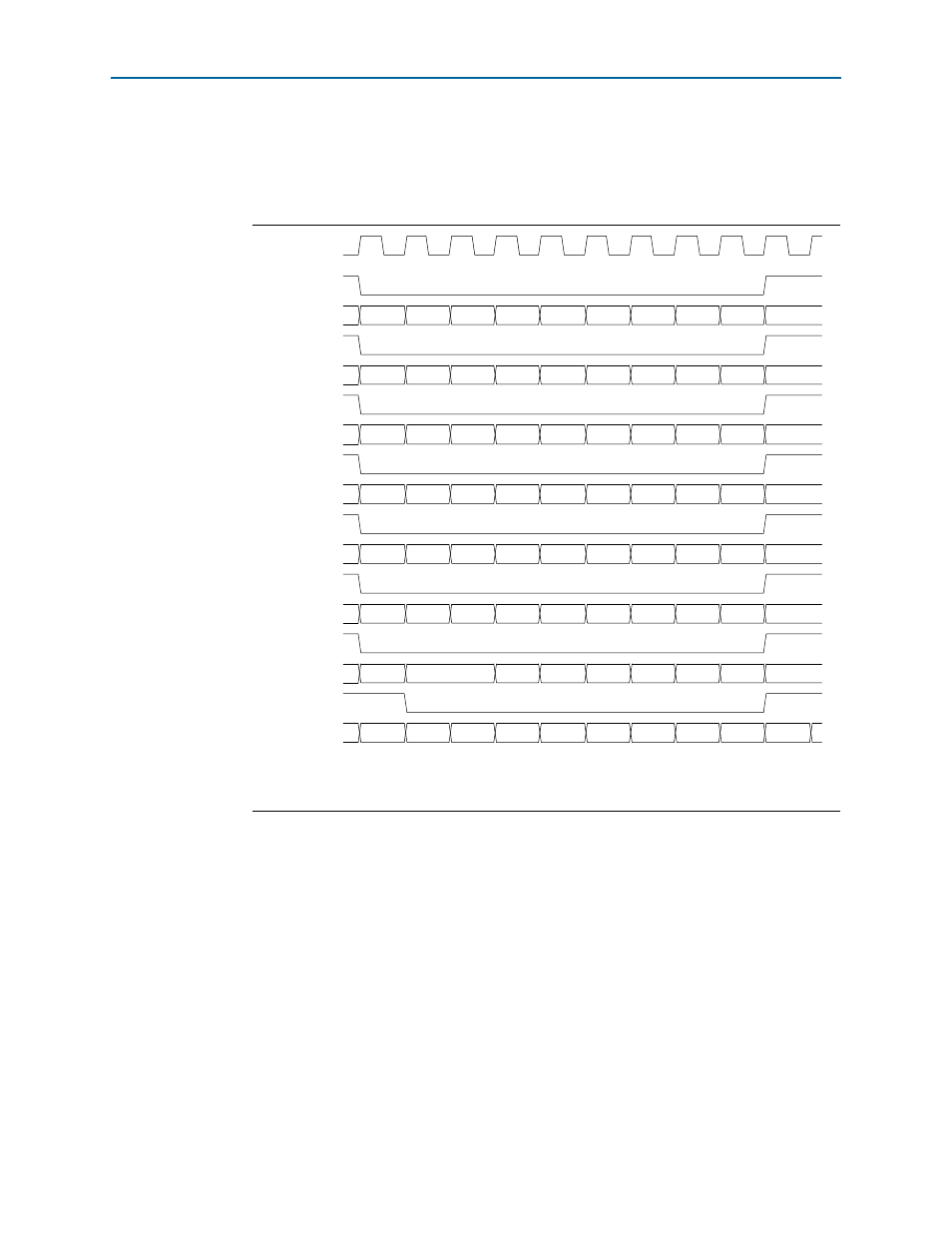

9.0.3.1. Timing Diagrams—SDR XGMII

The diagrams in this section show the timing for the SDR XGMII.

Figure 9–7

shows the timing for the SDR XGMII RX interface data bus.

When an error occurs, the control bit signal is asserted and the data during that clock

cycle is replaced by a control error character (FE).

Figure 9–7. SDR XGMII RX Interface Data Bus

Note to

Figure 9–7

:

(1) In the preamble passthrough mode, the MAC TX frame starts with a 1-byte START and a 7-byte client-defined

preamble.

rx_clk_clk

xgmii_rx_data[71]

xgmii_rx_data[70:63]

xgmii_rx_data[62]

xgmii_rx_data[61:54]

xgmii_rx_data[53]

xgmii_rx_data[52:45]

xgmii_rx_data[44]

xgmii_rx_data[43:36]

xgmii_rx_data[35]

xgmii_rx_data[34:27]

xgmii_rx_data[26]

xgmii_rx_data[25:18]

xgmii_rx_data[17]

xgmii_rx_data[16:9]

xgmii_rx_data[8]

xgmii_rx_data[7:0]

D5

(1)

CC

01

09

11

19

21

29

F4

EE

00

08

10

18

20

28

0A

EE

2E

07

0F

17

1F

27

B3

AA

00

06

0E

16

1E

26

4E

CC

EE

05

0D

15

1D

25

2D

88

AA

04

0C

14

1C

24

2C

55

(1)

CC

03

0B

13

1B

23

2B

FB

EE

88

02

0A

12

1A

22

2A

FD

55

(1)

55

(1)

55

(1)

55

(1)

55

(1)