Avalon-mm programming interface signals, Avalon-mm programming interface signals –12 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 131

9–12

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

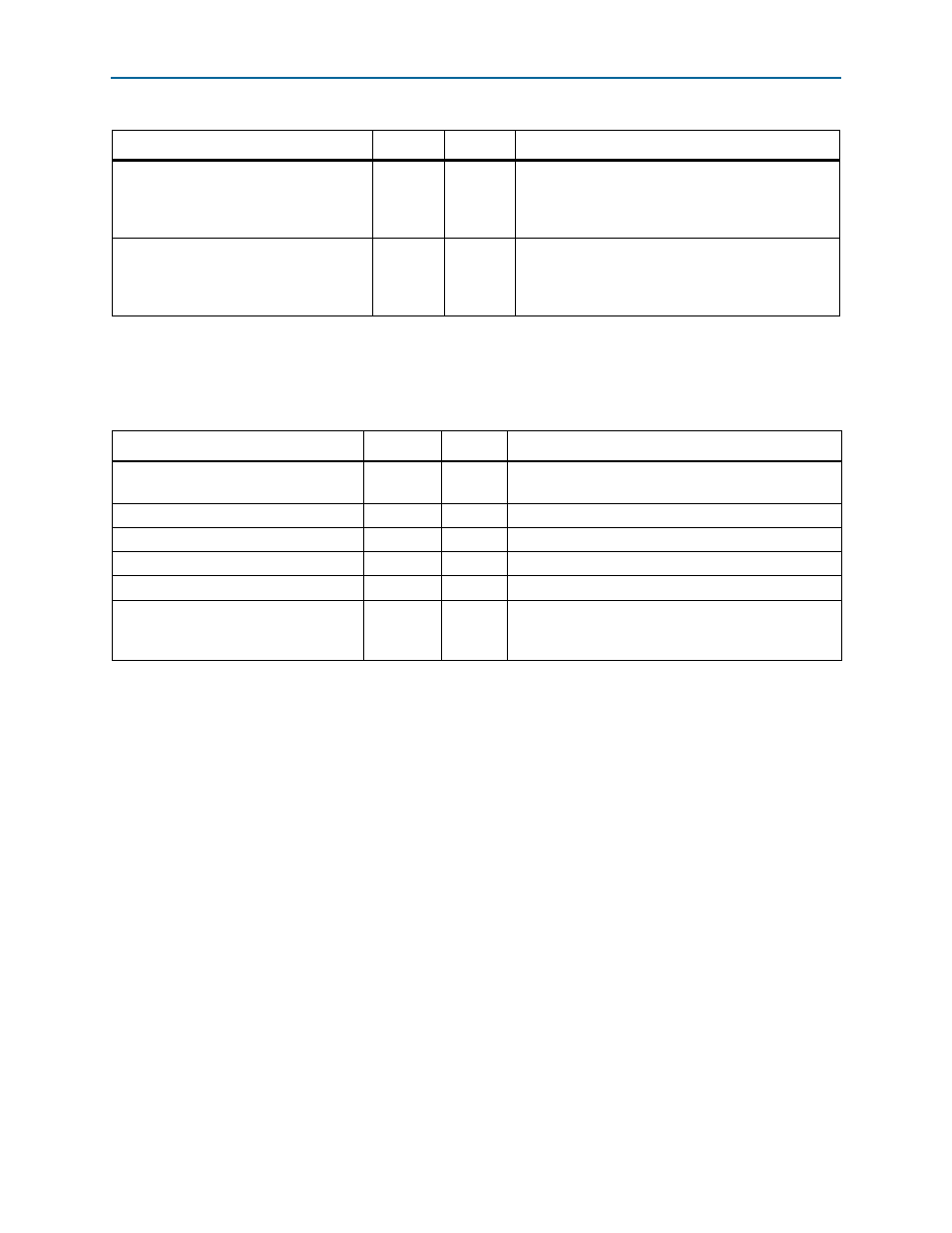

9.0.6. Avalon-MM Programming Interface Signals

Table 9–7

describes the Avalon-MM programming interface signals.

tx_clkena

Input

1

The TX clock enable provided by the PHY IP to the

MAC. This clock divides gmii_tx_clk_clk down to

25 MHz for 100 Mbps mode and 2.5 MHz for

10 Mbps mode.

tx_clkena_half_rate

Input

1

The TX half-clock enable provided by the PHY IP to

the MAC. This clock divides gmii_tx_clk_clk down

to 12.5 MHz for 100 Mbps mode and 1.25 MHz for

10 Mbps mode.

Table 9–6. MII Signals

Signal

Direction

Width

Description

Table 9–7. Avalon-MM CSR Interface Signals

Signal

Direction

Width

Description

csr_address[]

Input

13

Use this bus to specify the register address you want to

read from or write to.

csr_read

Input

1

Assert this signal to request a read.

csr_readdata[]

Output

32

Carries the data read from the specified register.

csr_write

Input

1

Assert this signal to request a write.

csr_writedata[]

Input

32

Carries the data to be written to the specified register.

csr_waitrequest

Output

1

When asserted, this signal indicates that the IP core is

busy and not ready to accept any read or write

requests.