Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 145

9–26

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

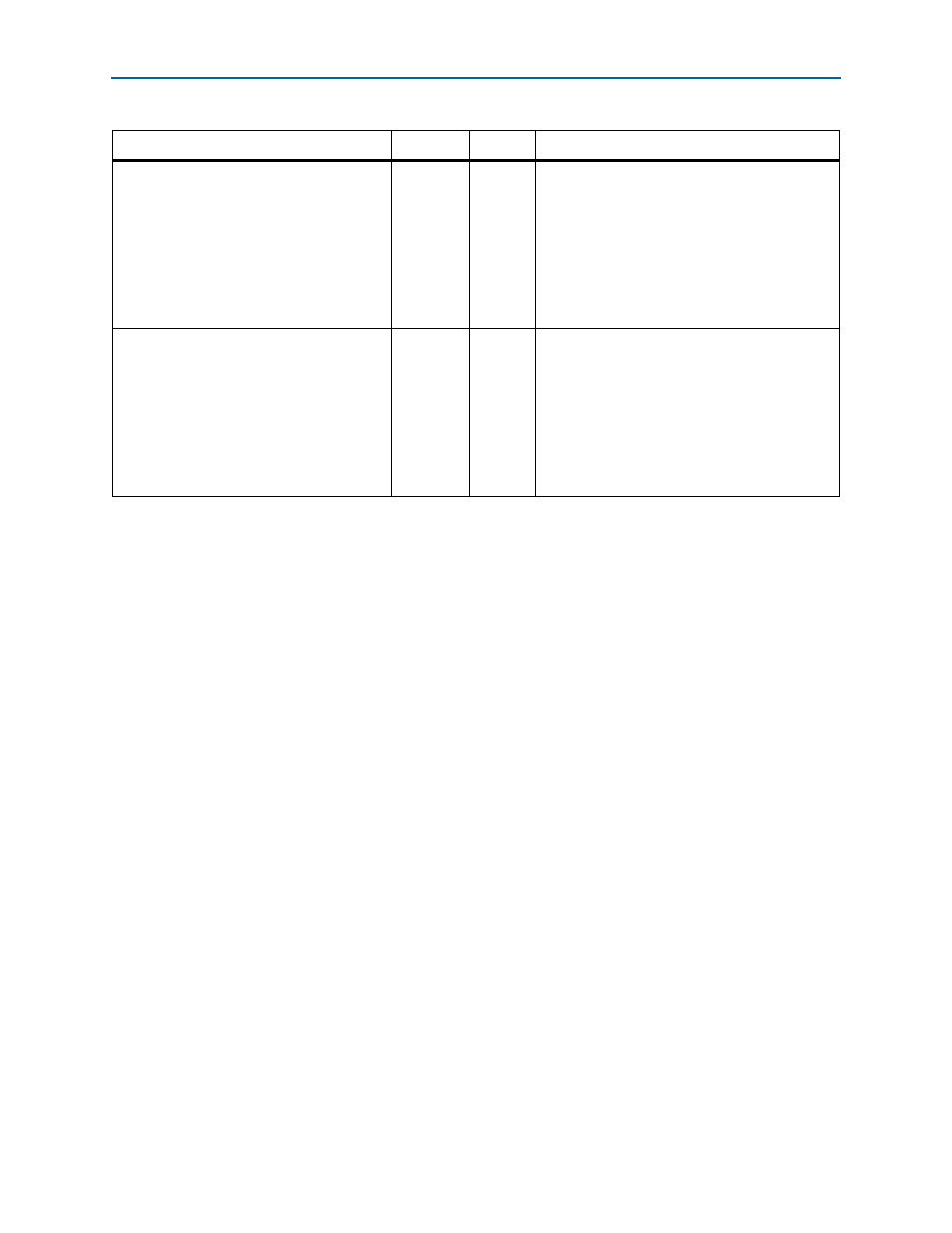

rx_path_delay_10g_data

(in 10 Gbps mode)

Input

16

Connect this bus to the Altera PHY IP. This bus

carries the path delay on the receive datapath. The

delay is measured between the physical network

and XGMII SDR. The delay is used to adjust the

ingress timestamp.

Consists of:

■

Bits 0 to 9: Fractional number of clock cycle

■

Bits 10 to 15: Number of clock cycle

rx_path_delay_1g_data

(in 1 Gbps, 10 Mbps, and 100 Mbps mode)

Input

22

Connect this bus to the Altera PHY IP. This bus

carries the path delay on the receive datapath. The

delay is measured between the physical network,

and GMII and MII. The delay is used to adjust the

ingress timestamp.

Consists of:

■

Bits 0 to 9: Fractional number of clock cycle

■

Bits 10 to 21: Number of clock cycle

Table 9–14. Path Delay Interface Signals

Signal

Direction

Width

Description