Interface signals, Chapter 9. interface signals – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 120

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

9. Interface Signals

This section describes the interface signals in all MAC variations.

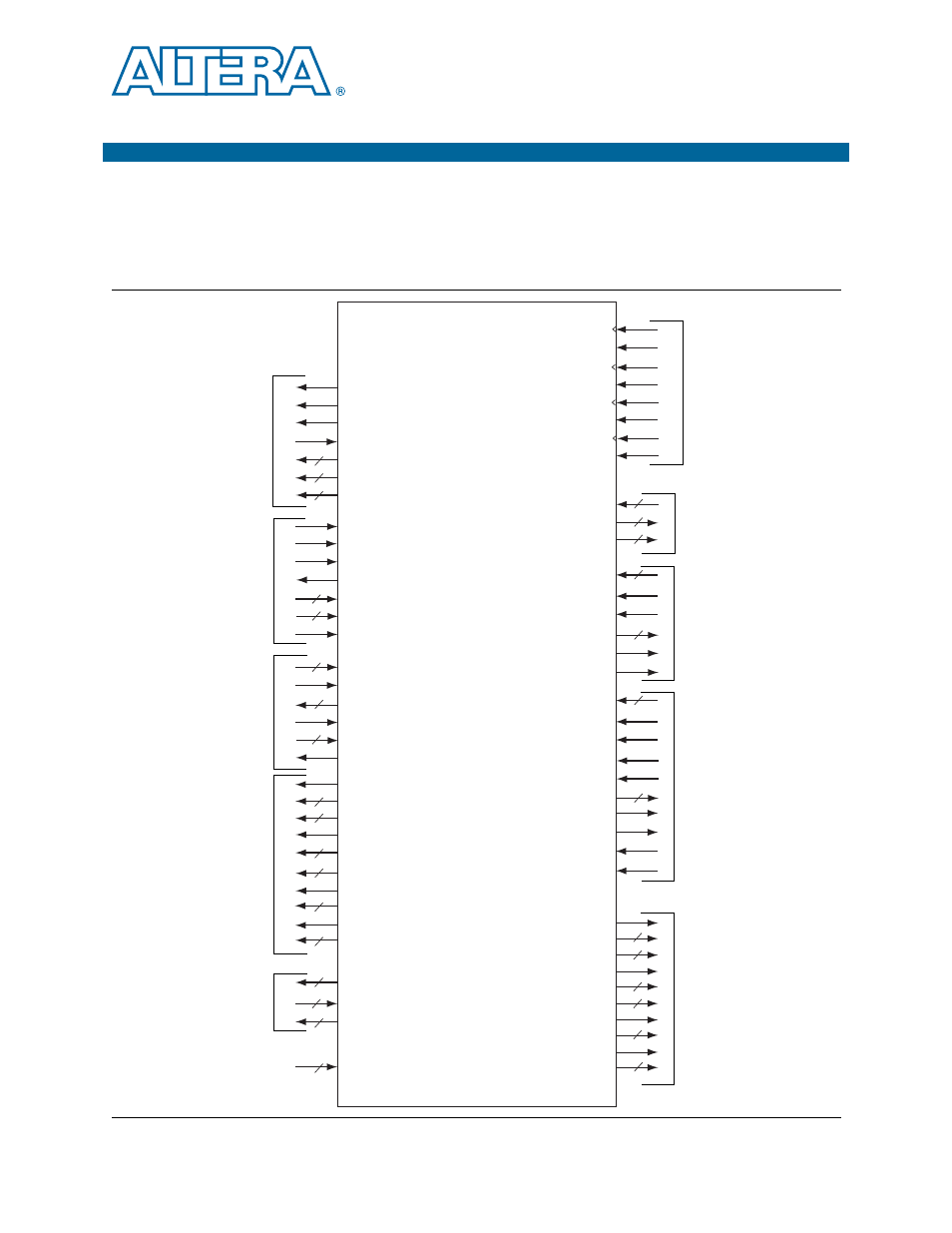

shows the interface signals for the MAC TX and RX variation.

Figure 9–1. 10M-10GbE MAC

SDR XGMII Signals

avalon_st_rx_startofpacket

avalon_st_rx_endofpacket

avalon_st_rx_valid

avalon_st_rx_ready

avalon_st_rx_data []

avalon_st_rx_empty []

avalon_st_rx_error []

avalon_st_tx_startofpacket

avalon_st_tx_endofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_data []

avalon_st_tx_empty []

avalon_st_tx_error

72

72

Clock and Reset

Signals

Avalon-ST Receive

Interface Signals

64

3

6

Avalon-ST Transmit

Interface Signals

3

64

10M-10GbE MAC

GMII Signals

gmii_rx_d []

gmii_rx_err

gmii_rx_dv

gmii_tx_en

gmii_tx_d []

gmii_tx_err

4

8

MII Signals

mii_rx_d []

mii_rx_err

mii_rx_dv

4

rx_clkena_half_rate

mii_tx_en

mii_tx_err

tx_clkena

tx_clkena_half_rate

rx_clkena

mii_tx_d []

8

avalon_st_pause_data []

avalon_st_rx_pfc_pause_data []

avalon_st_tx_pfc_gen_data []

Avalon-ST Pause

Signals

MAC Speed Control

Signal

2

16

8

avalon_st_rxstatus_valid

avalon_st_rxstatus_data []

avalon_st_rxstatus_error []

avalon_st_txstatus_error []

avalon_st_txstatus_valid

avalon_st_txstatus_data []

avalon_st_rx_pfc_status_valid

avalon_st_rx_pfc_status_data []

avalon_st_tx_pfc_status_valid

avalon_st_tx_pfc_status_data []

Avalon-ST Status

Signals

40

7

7

40

16

16

csr_address []

csr_readdata []

csr_write

csr_writedata []

csr_waitrequest

Avalon-MM Control

Interface Signals

csr_read

speed_sel[]

32

32

13

tx_clk_clk

tx_reset_reset_n

rx_clk_clk

rx_reset_reset_n

csr_clk_clk

csr_reset_reset_n

gmii_tx_clk_clk

gmii_rx_clk_clk

xgmii_tx_data []

xgmii_rx_data []

link_fault_status_xgmii_rx_data []

2

IEEE 1588v2

Interface

tx_egress_timestamp_64b_valid

4

tx_egress_timestamp_64b_fingerprint[]

tx_egress_timestamp_64b_data[]

64

tx_egress_timestamp_96b_valid

tx_egress_timestamp_96b_fingerprint[]

4

tx_egress_timestamp_96b_data[]

96

rx_ingress_timestamp_64b_valid

64

rx_ingress_timestamp_64b_data[]

rx_ingress_timestamp_96b_valid

rx_ingress_timestamp_96b_data[]

96

2