Reconfiguration bundle parameters, Base addresses – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 49

5–4

Chapter 5: 1G/10GbE MAC Design Example

1G/10GbE Design Example Components

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

1

To enable the Avalon-ST Single-Clock FIFO to operate in cut through mode,

turn off the Use store and forward parameter in the Avalon-ST Single

Clock FIFO

parameter editor.

■

PHY IP Reset Controller—configurable IP core that you can use to reset the

transceivers. Refer to the Transceiver PHY Reset Controller IP Core chapter in the

for more information.

■

Configure Reconfiguration Block—provides the Avalon-MM interface to drive the

reconfiguration bundle component to switch speed.

1

This component is required only if the automatic speed detection parameter

in the Backplane Ethernet 10GBASE-KR PHY is not enabled.

5.2.1. Reconfiguration Bundle Parameters

lists the parameters for the reconfiguration bundle block.

5.2.2. Base Addresses

Table 5–2

lists the design example components that you can configure to suit your

verification objectives. To configure the components, write to their registers using the

base addresses listed in the table and the register offsets described in the components'

user guides.

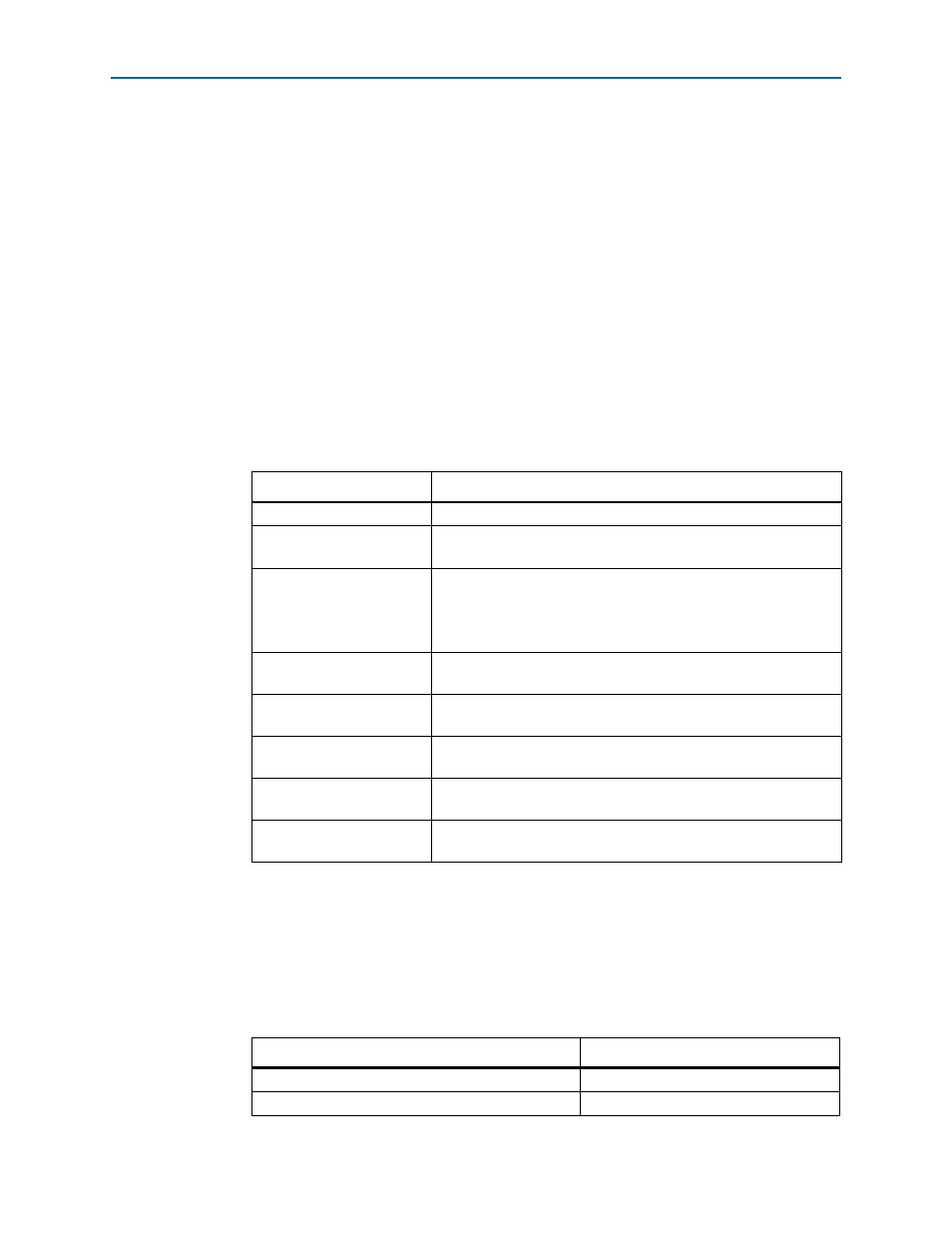

Table 5–1. Reconfiguration Bundle Parameters

Parameter

Description

PMA_RD_AFTER_WRITE

Always set this parameter to 0.

CHANNELS

The number of channels instantiated for the Backplane Ethernet

10GBASE-KR PHY IP.

PLLS

The number of PLLs.

If you turn on the 1G mode in the Backplane Ethernet 10GBASE-KR

PHY IP, this value will be two times the value of the CHANNELS

parameter.

SYNTH_1588_1G

Set this parameter to 1 if you use 1G mode with the 1588 options

turned on in the Backplane Ethernet 10GBASE-KR PHY IP.

SYNTH_1588_10G

Set this parameter to 1 if you use 10G mode with the 1588 options

turned on in the Backplane Ethernet 10GBASE-KR PHY IP.

KR_PHY_SYNTH_LT

Set this parameter to 1 if the Enable Link Training (LT) option is

turned on in the Backplane Ethernet 10GBASE-KR PHY IP.

KR_PHY_SYNTH_AN

Set this parameter to 1 if the Enable Auto Negotiation (AN) option is

turned on in the Backplane Ethernet 10GBASE-KR PHY IP.

KR_PHY_SYNTH_GIGE

Set this parameter to 1 if you use 1G mode in the Backplane Ethernet

10GBASE-KR PHY IP.

Table 5–2. Base Addresses of 1G/10GbE Design Example Components

Component

Base Address

1G/10GbE MAC Channel 0

0x00000

1G/10GbE MAC Channel 1

0x20000