Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 12

1–6

Chapter 1: About This IP Core

Performance and Resource Utilization

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

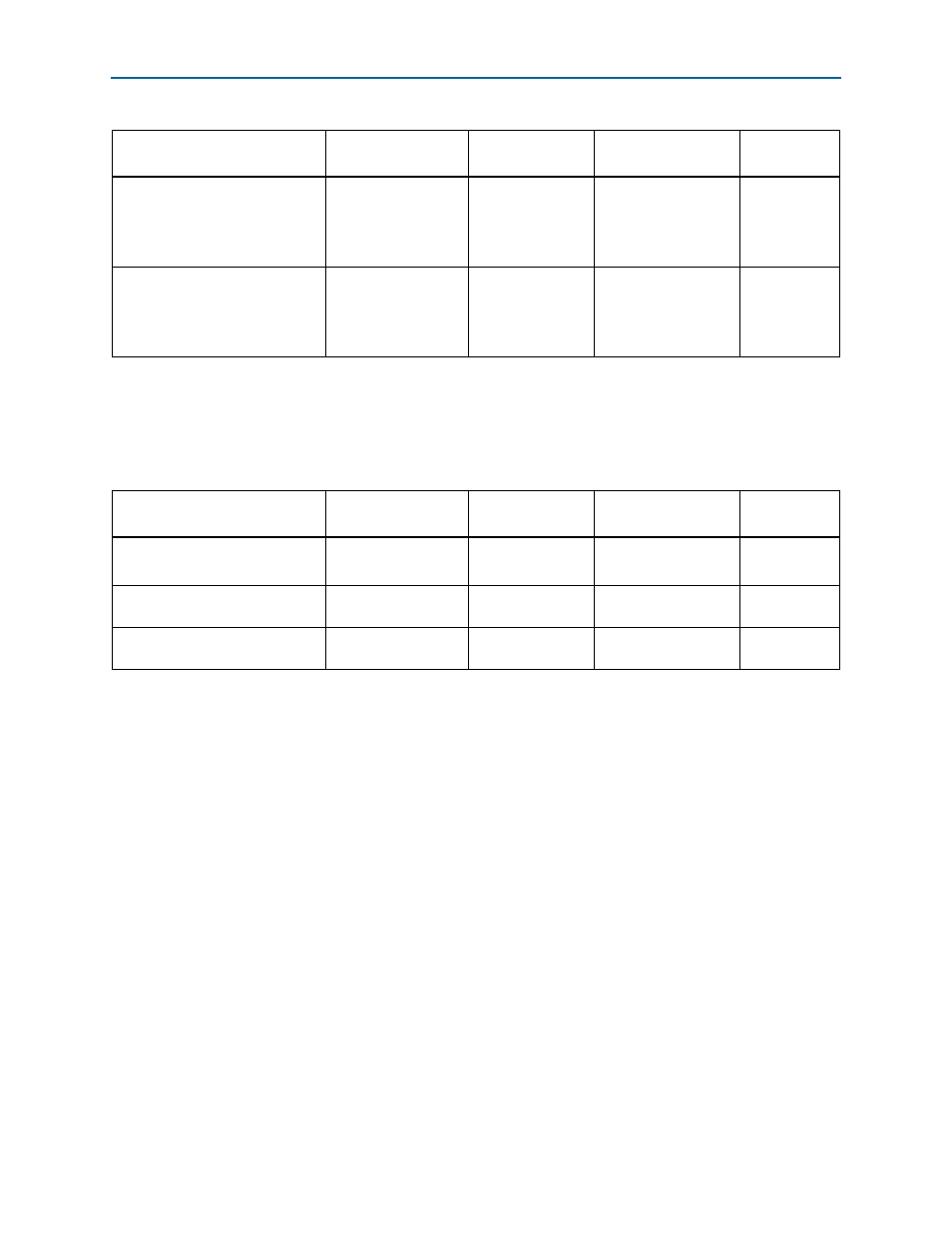

Table 1–8

provides the estimated performance and resource utilization of the

multi-speed 10M-10GbE MAC for the Stratix V device family. The estimates are

obtained by compiling the 10M-10GbE MAC with the Quartus II software targeting a

Stratix V GX (5SGXEA7H3F35C3) device with speed grade –3.

IEEE 1588v2 feature enabled with

2-step synchronization

■

Timestamping is enabled

■

ptp_1step is disabled

4,827

5,921

8

>156.25

IEEE 1588v2 feature enabled with

1-step and 2-step synchronization

■

Timestamping is enabled

■

ptp_1step is disabled

6,822

7,926

11

>156.25

Table 1–7. Stratix V Performance and Resource Utilization for 10GbE MAC (Part 2 of 2)

Settings

Combinational ALUTs

Dedicated Logic

Registers

Memory Block (M20K)

f

MAX

(MHz)

Table 1–8. Stratix V Performance and Resource Utilization for 10M-10GbE MAC

Settings

Combinational ALUTs

Dedicated Logic

Registers

Memory Block (M20K)

f

MAX

(MHz)

All options disabled

3,654

4,645

7

>156.25

All options enabled with

memory-based statistics counters

4,877

5,797

11

>156.25

All options enabled with

register-based statistics counters

7,313

7,544

7

>156.25