Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 103

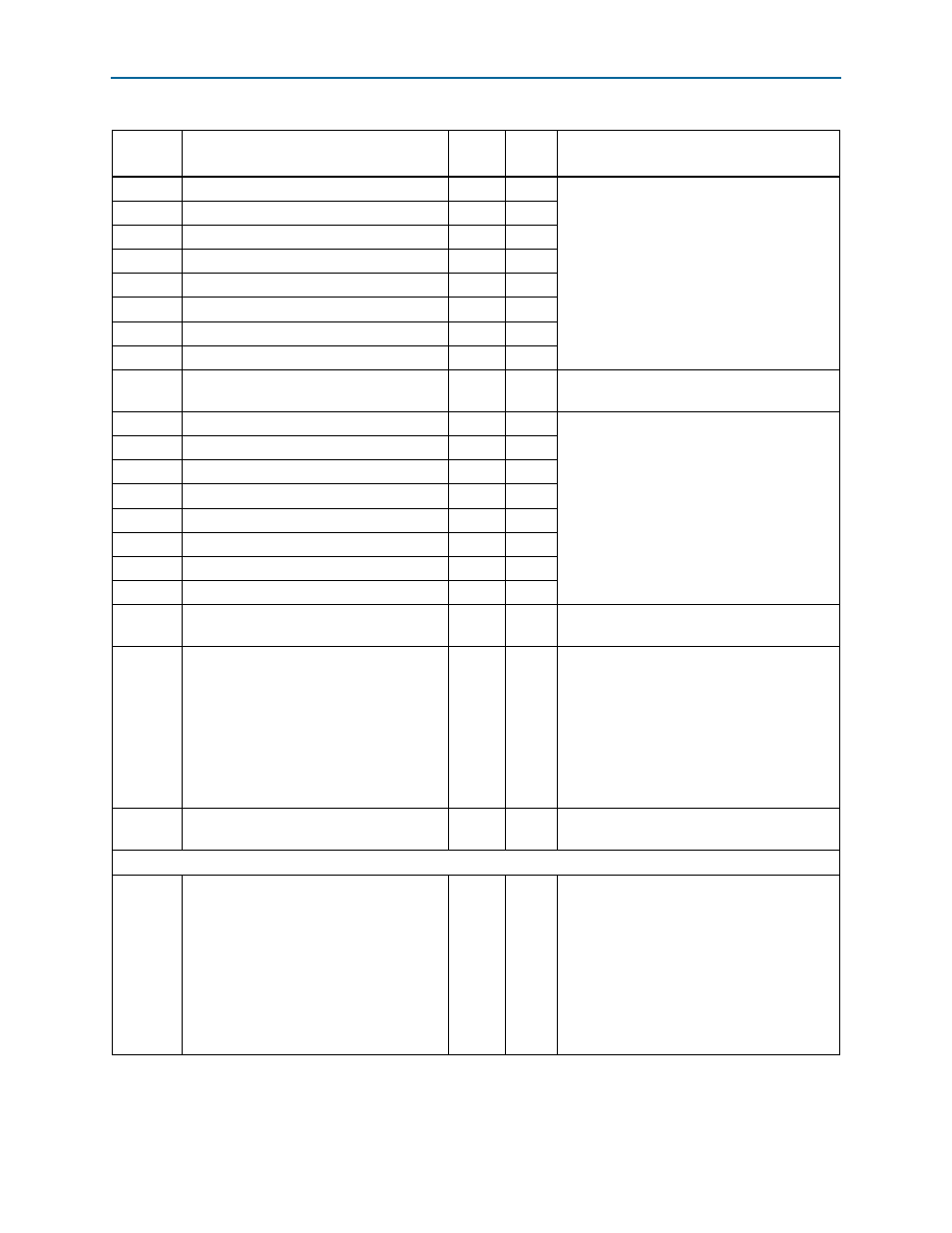

Chapter 8: Registers

8–9

MAC Registers

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

0x1180

pfc_pause_quanta_0

RW

0x0

pfc_pause_quanta_n

specifies the pause

length for priority queue n. The pause length is

in unit of pause quanta, where 1 pause quanta

= 512 bits time.

Bits 16 to 31 are reserved.

0x1181

pfc_pause_quanta_1

RW

0x0

0x1182

pfc_pause_quanta_2

RW

0x0

0x1183

pfc_pause_quanta_3

RW

0x0

0x1184

pfc_pause_quanta_4

RW

0x0

0x1185

pfc_pause_quanta_5

RW

0x0

0x1186

pfc_pause_quanta_6

RW

0x0

0x1187

pfc_pause_quanta_7

RW

0x0

0x1188 –

0x118F

Reserved

—

—

Reserved for future use.

0x1190

pfc_holdoff_quanta_0

RW

0x0

pfc_holdoff_quanta_n

specifies the gap

between consecutive XOFF requests for

priority queue n. The gap is in unit of holdoff

quanta, where 1 holdoff quanta = 512 bits

time.

Bits 16 to 31 are reserved.

0x1191

pfc_holdoff_quanta_1

RW

0x0

0x1192

pfc_holdoff_quanta_2

RW

0x0

0x1193

pfc_holdoff_quanta_3

RW

0x0

0x1194

pfc_holdoff_quanta_4

RW

0x0

0x1195

pfc_holdoff_quanta_5

RW

0x0

0x1196

pfc_holdoff_quanta_6

RW

0x0

0x1197

pfc_holdoff_quanta_7

RW

0x0

0x1198 –

0x119F

Reserved

—

—

Reserved for future use.

0x11A0

tx_pfc_priority_enable

RW

0x0

Enables PFC for a priority queue on the

transmit datapath.

■

Bit 0 to 7: Setting bit n in this register

enables PFC for priority queue n. For

example, setting

tx_pfc_priority_enable[0]

enables

PFC for priority queue 0.

■

Bits 8 to 31 are reserved.

0x11A1 –

0x11FF

Reserved

—

—

Reserved for future use.

TX Address Inserter (0x1200:0x127F)

0x1200

tx_addrins_control

RW

0x0

Address insertion on the transmit datapath.

■

Bit 0 configures address insertion.

0—Disables address insertion on the

transmit datapath.

1—Overwrites the source address field of

transmit frames with the address

configured in the tx_addrins_macaddr0

and tx_addrins_macaddr1 registers.

■

Bits 1 to 31 are reserved.

Table 8–2. MAC Registers (Part 8 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description