Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 38

3–20

Chapter 3: 10GbE MAC Design Examples

10GbE Design Example Compilation and Verification in Hardware

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

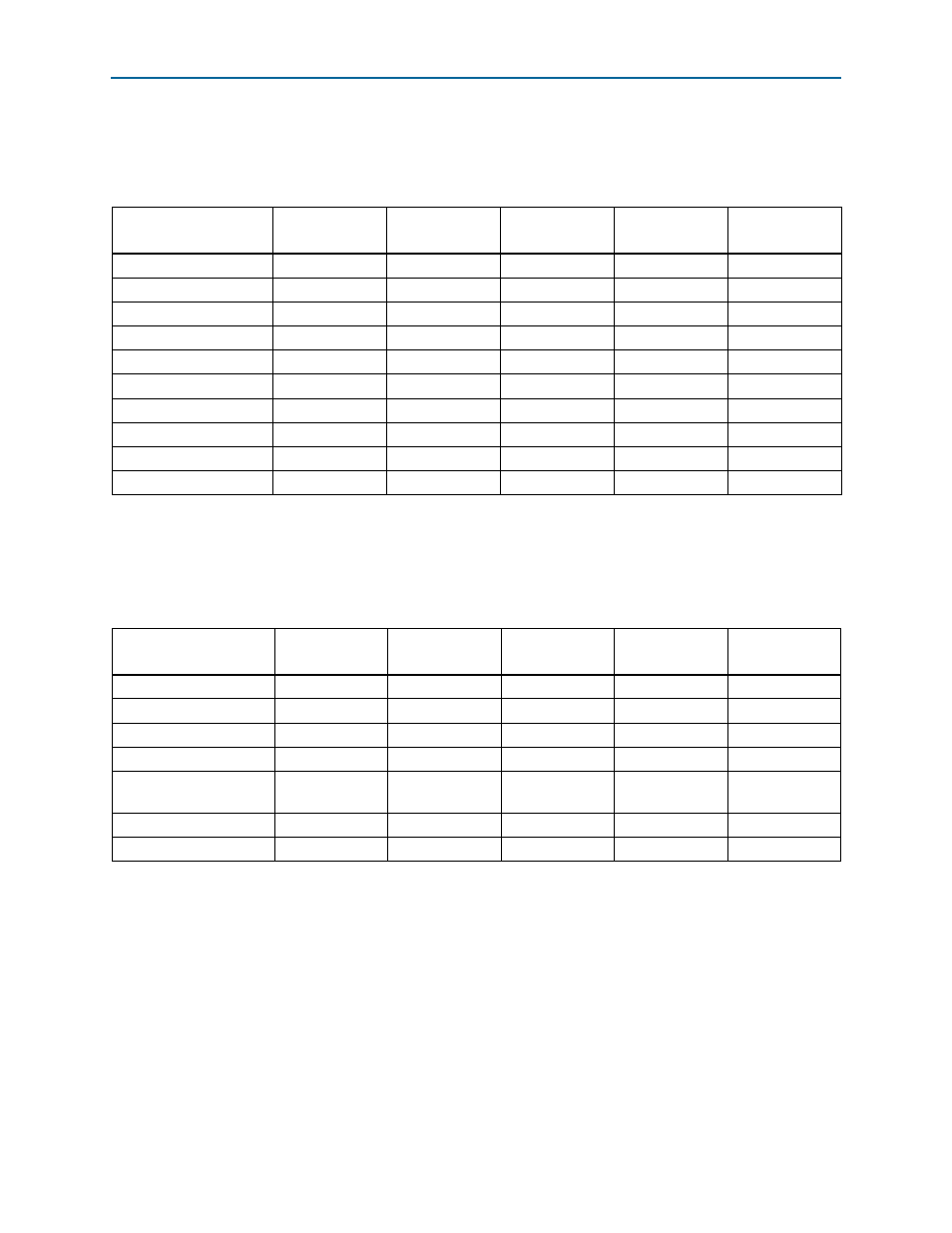

Table 3–9

provides the estimated performance and resource utilization of the 10GbE

design example obtained by compiling the design with the Quartus II software

targeting the Stratix V GX (5SGXEA7N2F40C2ES) device with speed grade –2.

Table 3–10

provides the estimated performance and resource utilization of the design

example with the IEEE 1588v2 feature enabled, obtained by compiling the design with

the Quartus II software targeting a Stratix V (5SGTMC5K2F40C2) device with speed

grade -2.

Table 3–9. Stratix V Performance and Resource Utilization

Components

Combinational

ALUTs

Memory ALUTs

Logic Registers

Memory Block

(M9K)

f

MAX

(MHz)

MAC

4,110

17

5,212

4

156.25

Loopback

290

0

187

4

156.25

RX SC FIFO

234

0

236

2

156.25

TX SC FIFO

220

0

246

2

156.25

MDIO

115

0

146

0

156.25

10GBASE-R PHY

112

0

114

0

156.25

JTAG Master

519

0

508

1

156.25

Address Swapper

66

0

74

0

156.25

Qsys Fabric

441

0

679

0

156.25

Total Resource Utilization

6,107

0

7,402

13

156.25

Table 3–10. Stratix V Performance and Resource Utilization with IEEE 1588v2 Feature

Components

Combinational

ALUTs

Logic Registers

Memory Block

(M20K)

DSP Block

f

MAX

(MHz)

MAC 6,822

7,459

10

2

156.25

Loopback

291

264

4

0

156.25

10GBASE-R PHY

1,066

1,675

6

0

156.25

Time-of-Day (ToD) Clock

812

2,268

0

0

156.25

Transceiver

Reconfiguration

1,245

871

6

0

156.25

Qsys Fabric

83

73

0

0

156.25

Total Resource Utilization

10,319

12,610

26

2

156.25