Timing diagrams—avalon-st receive interface, Timing diagrams—avalon-st receive interface –6 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 125

9–6

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

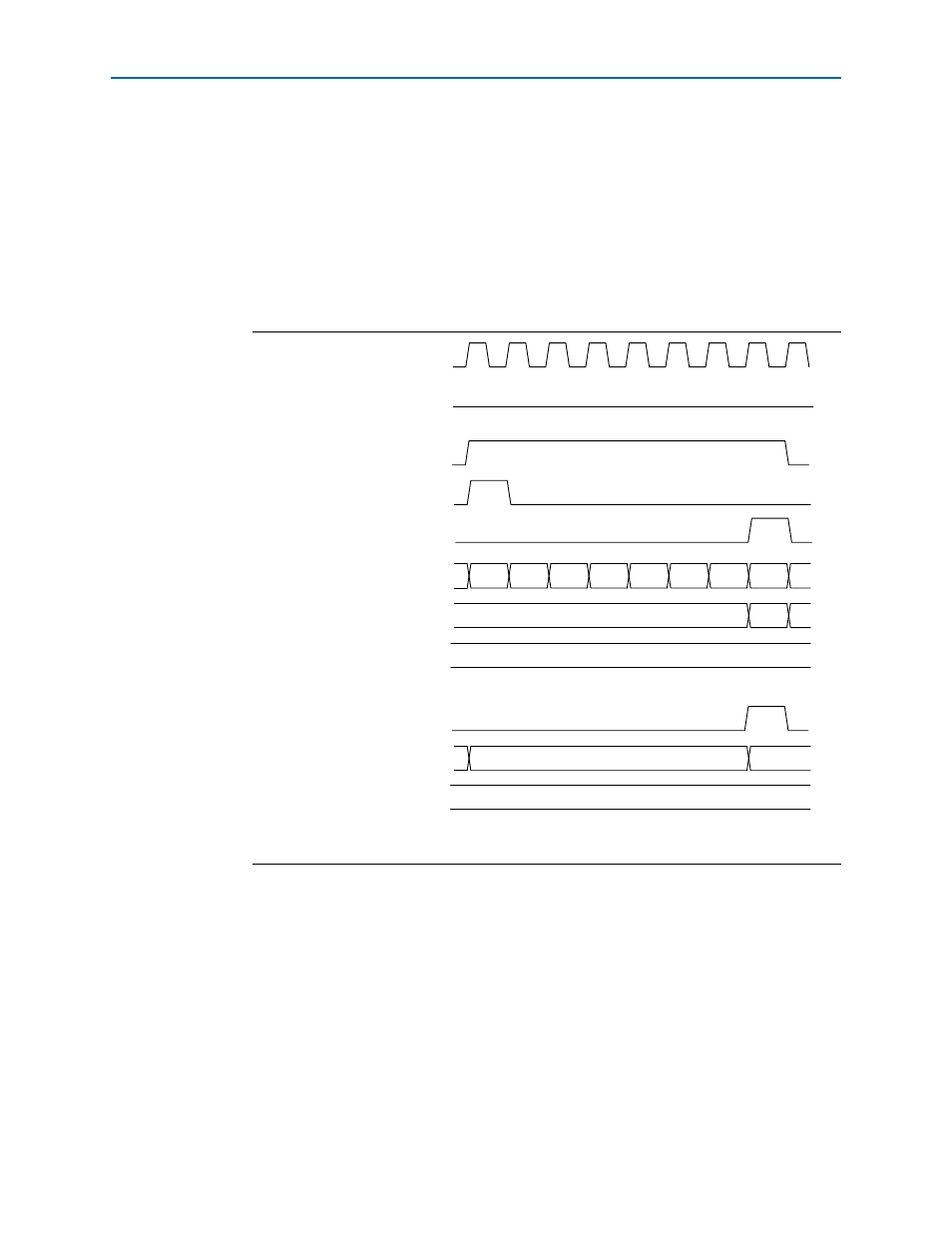

9.0.2.2. Timing Diagrams—Avalon-ST Receive Interface

The diagrams in this section show the timing on the Avalon-ST receive interface.

The Avalon-ST receive interface avalon_st_rx_startofpacket signal is asserted to

indicate the start of a new frame. On the same rising edge of rx_clk_clk, the

avalon_st_rx_valid

signal is also asserted to qualify the transmit data on the

avalon_st_rx_data[63:0]

bus. The end of the receive packet is indicated by the

avalon_st_rx_endofpacket

signal.

Figure 9–5

shows the timing for the Avalon-ST receive interface with a good frame.

When the MAC RX receives an undersized frame, it sets the avalon_st_rx_error[2]

bit to 1. When an overflow occurs, the avalon_st_rx_ready signal is deasserted to

backpressure the Avalon-ST receive interface, and the MAC RX sets the

avalon_st_rx_error[5]

bit to 1. The error signals are sampled when

avalon_st_rx_endofpacket

and avalon_st_rx_valid signals are asserted.

For more information about the error signals in the Avalon-ST receive and status

interface, refer to

Table 9–3 on page 9–3

and

Table 9–8 on page 9–13

.

Figure 9–5. Avalon-ST Receive

Note to

Figure 9–5

:

(1) n indicates the number of symbols that are empty during the cycles that mark the end of a frame.

rx_clk_clk

avalon_st_rx_startofpacket

avalon_st_rx_endofpacket

avalon_st_rxstatus_valid

avalon_st_rx_valid

avalon_st_rx_ready

avalon_st_rxstatus_data [38:0]

avalon_st_rx_data [63:0]

avalon_st_rx_empty [2:0]

avalon_st_rxstatus_error [6:0]

avalon_st_rx_error [5:0]

n

0

0

0

(1)