D.2. block diagram – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 167

D–2

Appendix D: ToD Synchronizer

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

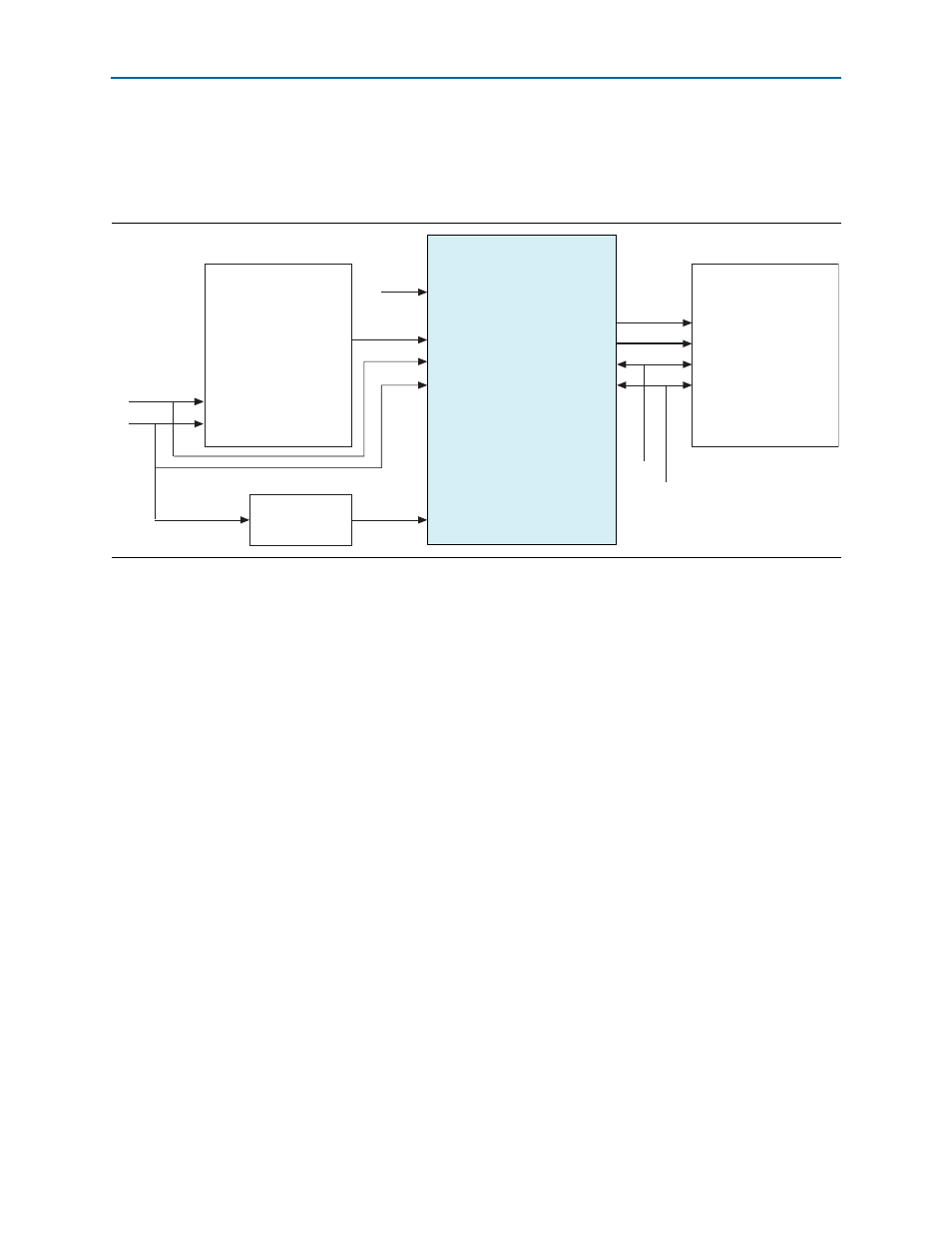

D.2. Block Diagram

Figure D–1

shows the connections between the ToD Synchronizer, master ToD, slave

ToD, and sampling clock PLL.

The ToD Synchronizer block diagram comprises the following components::

■

Master TOD clock domain—consists of three interfaces: clk_master,

reset_master

, and tod_master_data.

■

Slave TOD clock domain—consists of five interfaces: clk_slave, reset_slave,

tod_slave_valid

, tod_slave_data, and start_tod_sync.

■

Sampling clock PLL—consists of the clk_domain interface.

The Tod Synchronizer module synchronizes the master ToD clock domain with the

slave ToD clock domain. The dual-clock FIFO in the Tod Synchronizer block takes in

the time of day from the master ToD clock domain and transfers it to the slave ToD

clock domain. The slave ToD then will load the synchronized time of day into its own

internal counter, which then increments based on the new value.

As the ToD transfer is in progress, the master ToD domain keeps incrementing. When

the ToD reaches the slave ToD clock domain and is ready to be loaded, it is much

slower than the master ToD domain. To achieve high accuracy synchronization, the

latency caused by the transfer must be reflected in the synchronized ToD.

The sampling clock PLL (clk_sampling) samples the FIFO fill level and calculates the

latency through the FIFO. For better accuracy, the sampling clock must be derived

from the master (clk_master) or slave (clk_slave) clock domain using a PLL.

If you use the recommended sampling clock frequency, the ToD Synchronizer module

takes 64 clock cycles of sampling clock for every newly synchronized ToD to be valid

at the output port.

Figure D–1. Connection between ToD Synchronizer, Master ToD, Slave ToD, and Sampling Clock PLL

Slave ToD

time_of_day_96b_load_valid

time_of_day_96b_load_data

period_rst_n

period_clk

ToD Synchronizer

tod_master_data

reset_master

clk_master

tod_slave_valid

Synchronization valid

Synchronization ToD

tod_slave_data

reset_slave

clk_slave

clk_sampling

start_tod_sync

Master ToD

PLL

time_of_day_96b

Master ToD

1’b1

Sampling clock

Master reset

Slave reset

Master clock

Slave clock

period_rst_n

period_clk