1g/10gbe design example components, 1g/10gbe design example components –2 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 47

5–2

Chapter 5: 1G/10GbE MAC Design Example

1G/10GbE Design Example Components

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

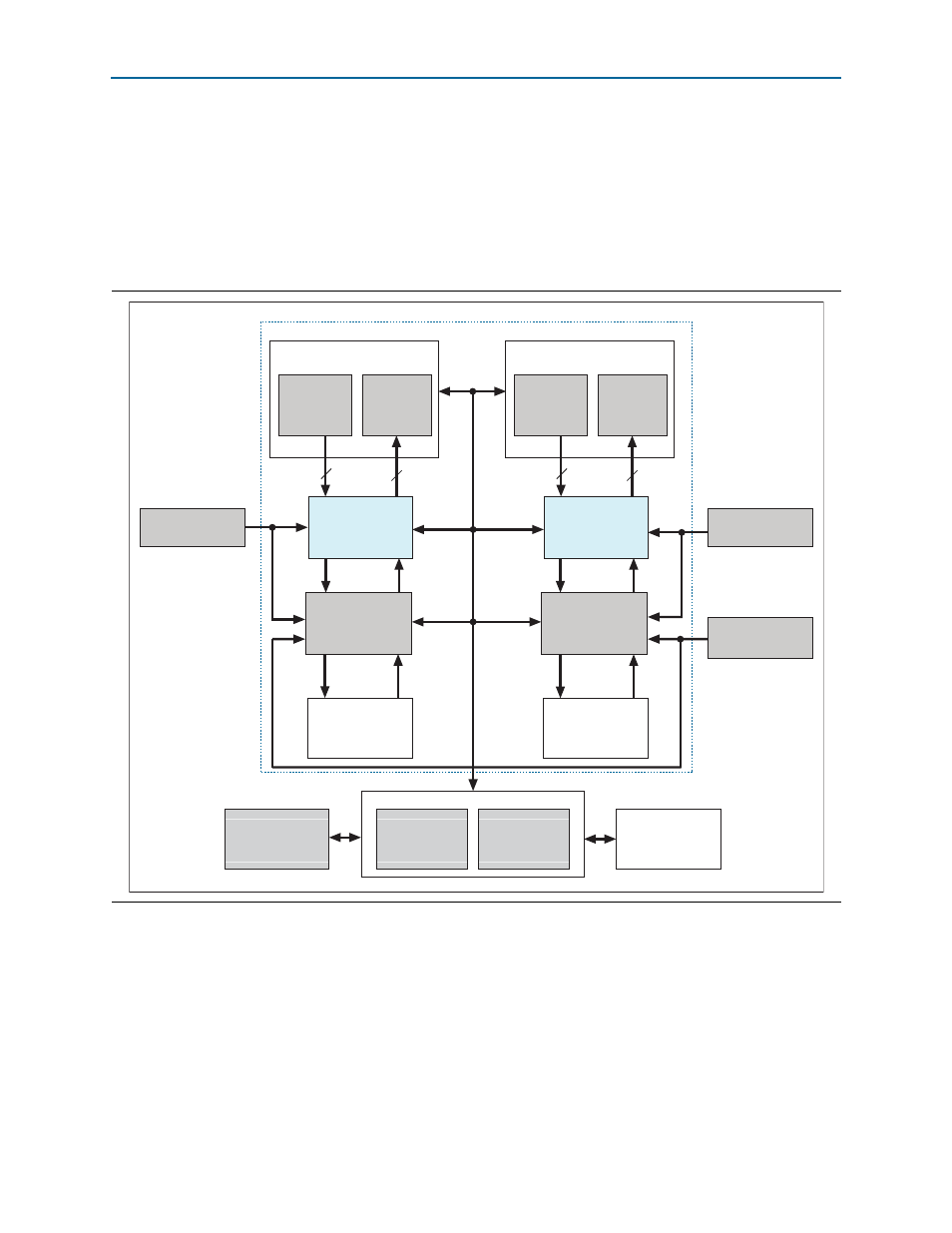

5.2. 1G/10GbE Design Example Components

You can use the 1G/10GbE MAC IP core design example to simulate a complete

1G/10GbE design in an Altera FPGA. You can compile the design example using the

simulation files generated by the Quartus II software and program the targeted Altera

device after a successful compilation.

shows the block diagram of a two-channel 1G/10GbE design example.

Figure 5–1. Two-Channel 1G/10GbE Design Example Block Diagram

System Console

(for Debugging)

Client Application

(Configuration, Status,

and Statistics)

JTAG to Avalon

Master Bridge

Pipeline Bridge

Configuration and Debugging Tools

PHY IP

Reset Controller

PHY IP

Reset Controller

1G/10GbE MAC

10GBASE-KR PHY

External PHY

64-Bit

Avalon-ST

GIGE/

10GBASE-R

TX FIFO

Buffer

RX FIFO

Buffer

Avalon-ST Single-Clock FIFO

64

64

1G/10GbE MAC

10GBASE-KR PHY

External PHY

64-Bit

Avalon-ST

GIGE/

10GBASE-R

TX FIFO

Buffer

RX FIFO

Buffer

Avalon-ST Single-Clock FIFO

64

64

Reconfiguration

Bundle

Altera FPGA