Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 61

6–2

Chapter 6: 10M-10GbE MAC with IEEE 1588v2 Design Example

10M-10GbE MAC with IEEE 1588v2 Design Example Components

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

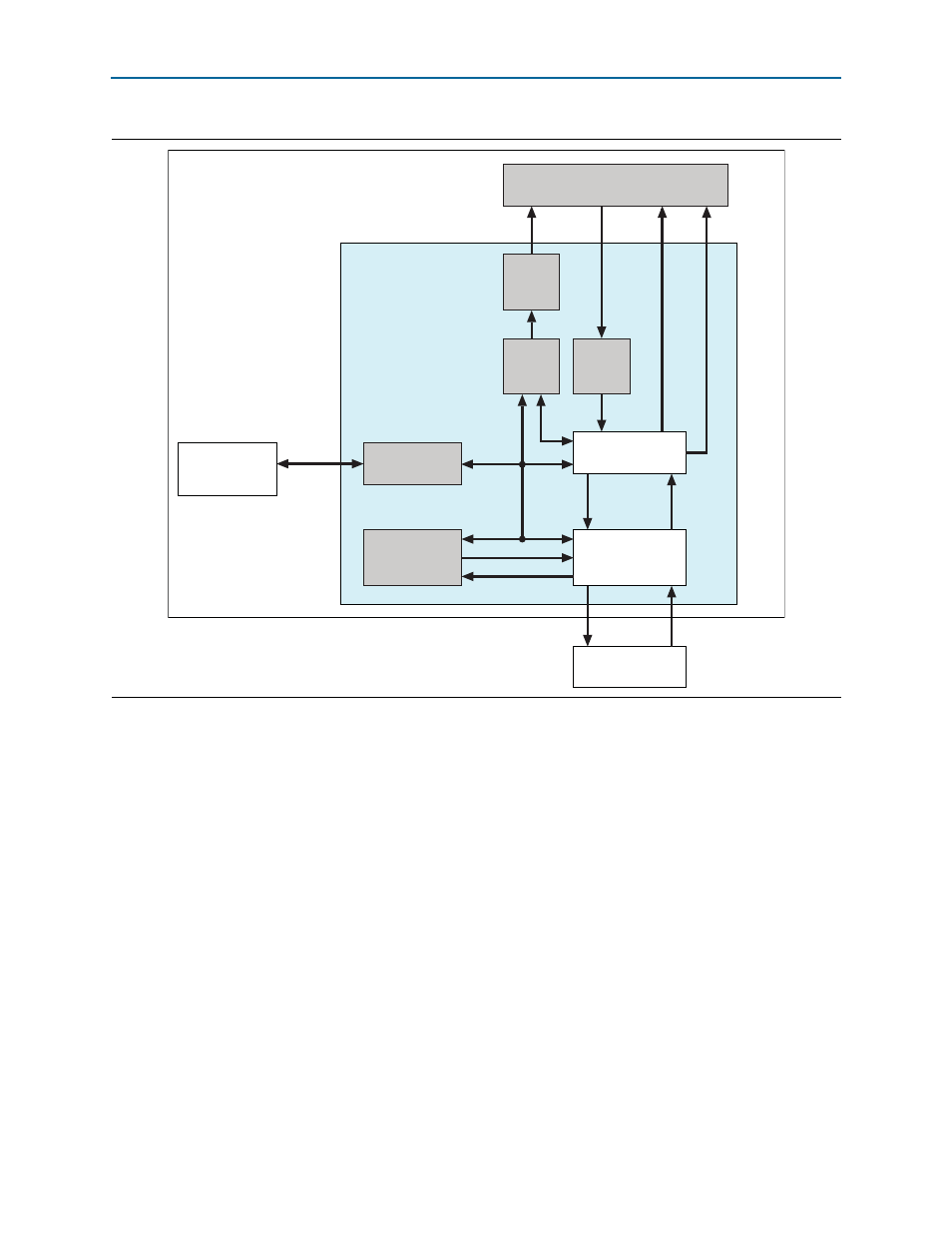

The 10M-10GbE MAC with IEEE 1588v2 design example comprises the following

components:

■

Altera Ethernet 10M-10GbE design example—the default 1G/10G design that has

the following parameter settings:

■

10M-10GbE Ethernet MAC—the MAC IP core with IEEE 1588v2 option

enabled.

■

MDIO and FIFO features turned off.

■

Backplane Ethernet 10GBASE-KR PHY—the PHY IP core with IEEE 1588v2 option

enabled.

■

Reconfiguration Bundle—comprises the reconfiguration controller that switches

the speed between 1 Gbps and 10 Gbps, and the management ROM that stores

MIF information for 1/10GbE PHY or HSSI or hard PCS. This block arbitrates the

access to the reconfiguration controller and requests the reconfiguration controller

to start streaming MIF information.

■

Ethernet Packet Classifier—decodes the packet type of incoming PTP packets and

returns the decoded information to the 10M-10GbE MAC.

Figure 6–1. 10M-10GbE MAC with IEEE 1588v2 Design Example Block Diagram

Ethernet

Packet

Classifier

Pulse Per

Second

Module

Time of

Day

Clock

Time of Day

1M/100M/1G/10G MAC

Avalon MM Master

Translator

Client Application

(Configuration,

Status & Statistics)

Reconfiguration

Bundle

10GBASE-KR PHY

External PHY

10GBASE-KR

72-Bit SDR

XGMII/10-bits

GMII

64-Bit

Avalon ST

Time

of Day

32-Bit

Avalon MM

Reconfiguration

32-Bit

Avalon MM

64-Bit

Avalon ST

Pulse Per

Second

Timestamp &

Fingerprint

Client Application

Altera FPGA

Design Example