B.5.1. avalon-mm control interface signal, B.5.2. avalon-st transmit interface signal – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 159

Appendix B: Time-of-Day (ToD) Clock

B–3

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

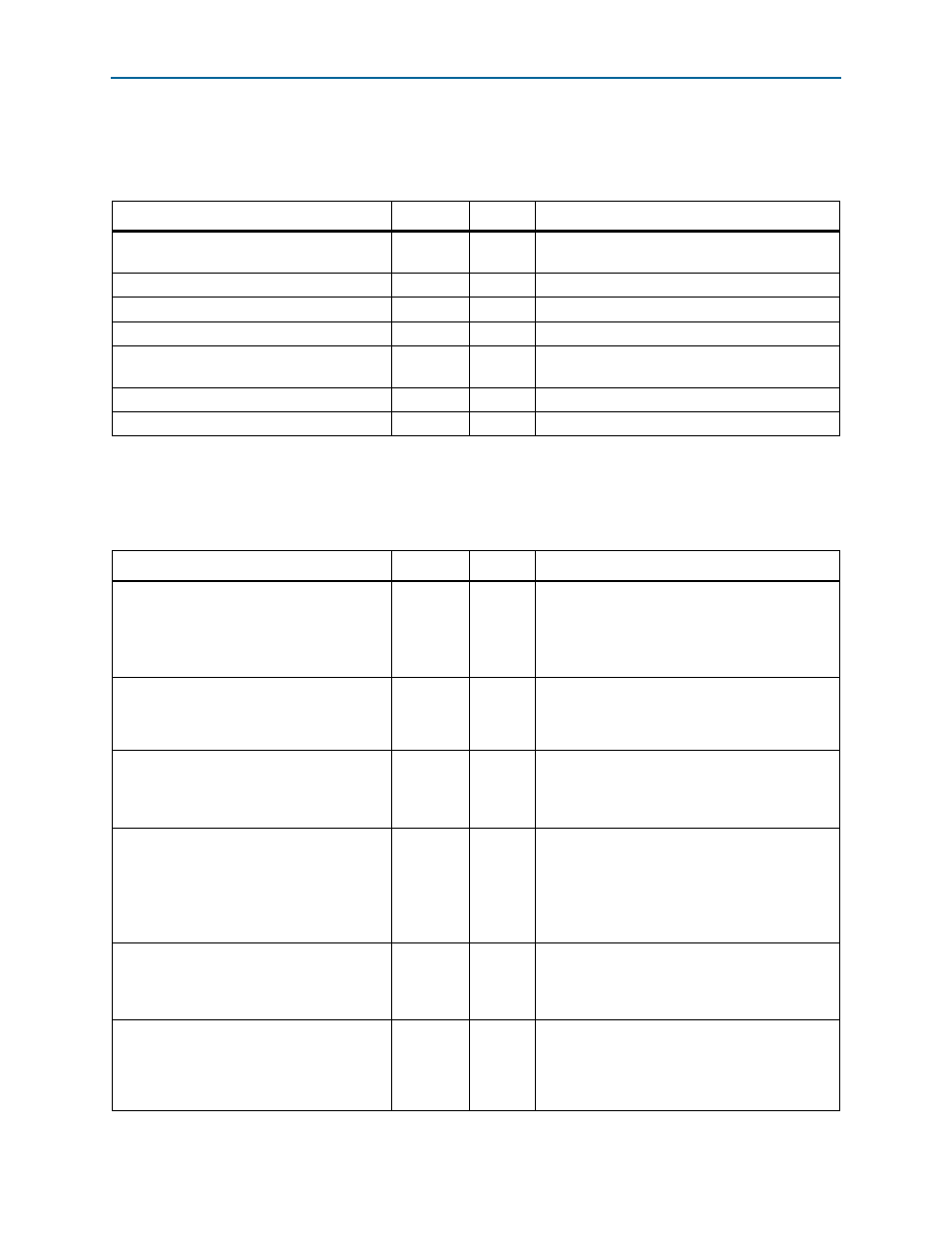

B.5.1. Avalon-MM Control Interface Signal

Table B–4

describes the Avalon-MM control interface signals for the ToD clock.

B.5.2. Avalon-ST Transmit Interface Signal

Table B–5

describes the Avalon-ST transmit interface signals for the ToD clock.

Table B–4. Avalon-MM Control Interface Signals for ToD Clock

Signal

Direction

Width

Description

csr_address[]

Input

2

Use this bus to specify the register address you

want to read from or write to.

csr_read

Input

1

Assert this signal to request a read.

csr_readdata[]

Output

32

Carries the data read from the specified register.

csr_write

Input

1

Assert this signal to request a write.

csr_writedata[]

Input

32

Carries the data to be written to the specified

register.

clk

Input

1

Register access reference clock.

rst_n

Input

1

Assert this signal to reset clk.

Table B–5. Avalon-ST Transmit Interface Signals for ToD Clock (Part 1 of 2)

Signal

Direction

Width

Description

time_of_day_96[]

Output

96

Timestamp from the ToD clock

■

Bits 0 to 15: 16-bit fractional nanosecond field

■

Bits 16 to 47: 32-bit nanosecond field

■

Bits 48 to 95: 48-bit second field

time_of_day_64[]

Output

64

Timestamp from the ToD clock

■

Bits 0 to 15: 16-bit fractional nanosecond field

■

Bits 16 to 63: 48-bit nanosecond field

time_of_day_96b_load_valid

Input

1

Indicates that the synchronized ToD is valid. Every

time you assert this signal, the synchronized ToD

is loaded into the ToD clock. Assert this signal for

only one clock cycle.

time_of_day_96b_load_data[]

Input

96

Loads 96-bit synchronized ToD from master ToD

clock to slave ToD clock within 1 clock cycle.

■

Bits 0 to 15: 16-bit fractional nanosecond field

■

Bits 16 to 63: 32-bit nanosecond field

■

Bits 64 to 95: 48-bit second field

time_of_day_64b_load_valid

Input

1

Indicates that the synchronized ToD is valid. Every

time you assert this signal, the synchronized ToD

is loaded into the ToD clock. Assert this signal for

only one clock cycle.

time_of_day_64b_load_data[]

Input

64

Loads 64-bit synchronized ToD from master ToD

clock to slave ToD clock within 1 clock cycle.

■

Bits 0 to 15: 16-bit fractional nanosecond field

■

Bits 16 to 63: 48-bit nanosecond field