D. tod synchronizer, D.1. device family support, Appendix d. tod synchronizer – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 166

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

D. ToD Synchronizer

The ToD Synchronizer provides a high accuracy synchronization of time of day from a

master ToD clock to a slave ToD clock. This synchronizer provides more user

flexibility for your design.

The IEEE 1588v2 specifies multiple type of PTP devices, which include the following

clocks:

■

ordinary clock

■

boundary clock

■

transparent clock

■

peer to peer transparent clock

Some of these PTP devices, boundary clock for example, consists of multiple ports

that act as master or slave in the IEEE 1588v2 system. All these ports may share a

common system clock or have its own individual clock. If every port has an

individual ToD running on its own clock, then you must implement a method to

instantiate one ToD clock as the master and the rest of the ToD clocks synchronized to

this master ToD clock.

For this purpose, Altera provides the ToD synchronizer module. This module

synchronizes a master ToD and a slave ToD in the following conditions:

■

Master and slave ToD clocks are in the same frequency within the range of

125 MHz and 156.25 MHz, but different phase.

■

Master and slave ToD clocks are same in the same frequency within the range of

125 MHz and 156.25 MHz, but different PPM.

■

Master and slave ToD clocks are in different frequencies (25 MHz or 156.25 MHz).

D.1. Device Family Support

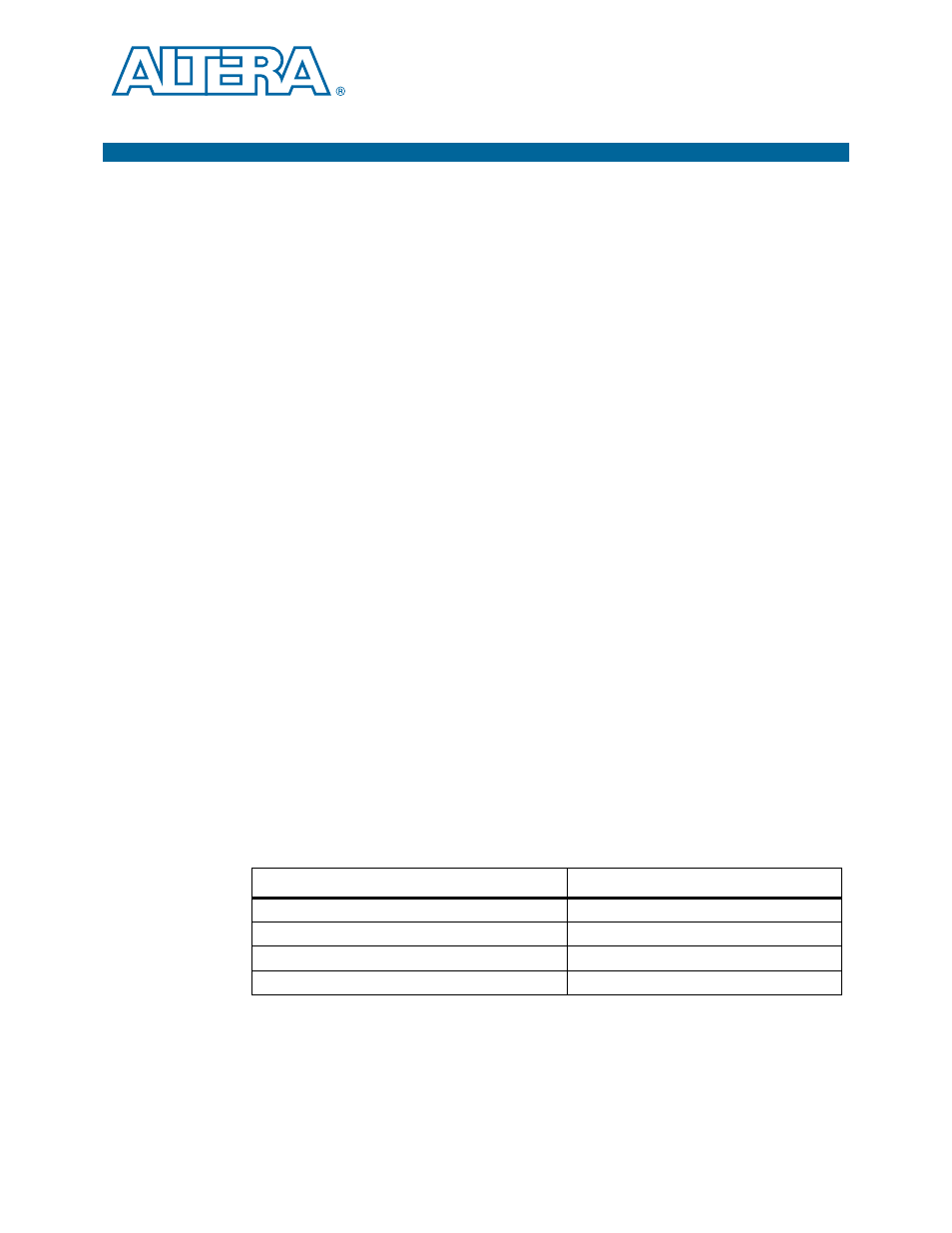

Table D–1

shows the level of support offered by the ToD clock for each Altera device

family.

Table D–1. Device Family Support

Device Family

Support

Arria V GX/GT/GZ/SOC

Preliminary

Cyclone V/SOC

Preliminary

Stratix V GX/GT

Preliminary

Other device families

No support