Timing diagrams—avalon-st transmit interface, Timing diagrams—avalon-st transmit interface –3 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 122

Chapter 9: Interface Signals

9–3

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

Table 9–3

describes the Avalon-ST receive signals.

9.0.2.1. Timing Diagrams—Avalon-ST Transmit Interface

The diagrams in this section shows the timing and the mapping on the Avalon-ST

transmit interface.

The client asserts the avalon_st_tx_startofpacket signal to indicate the beginning of

the transmit packet. On the same rising edge of tx_clk_clk, the client asserts the

avalon_st_tx_valid

signal to qualify the transmit data on the

avalon_st_tx_data[63:0]

bus. At the end of the packet, the avalon_st_tx_empty

[2:0]

signal specifies the number of bytes that are empty.

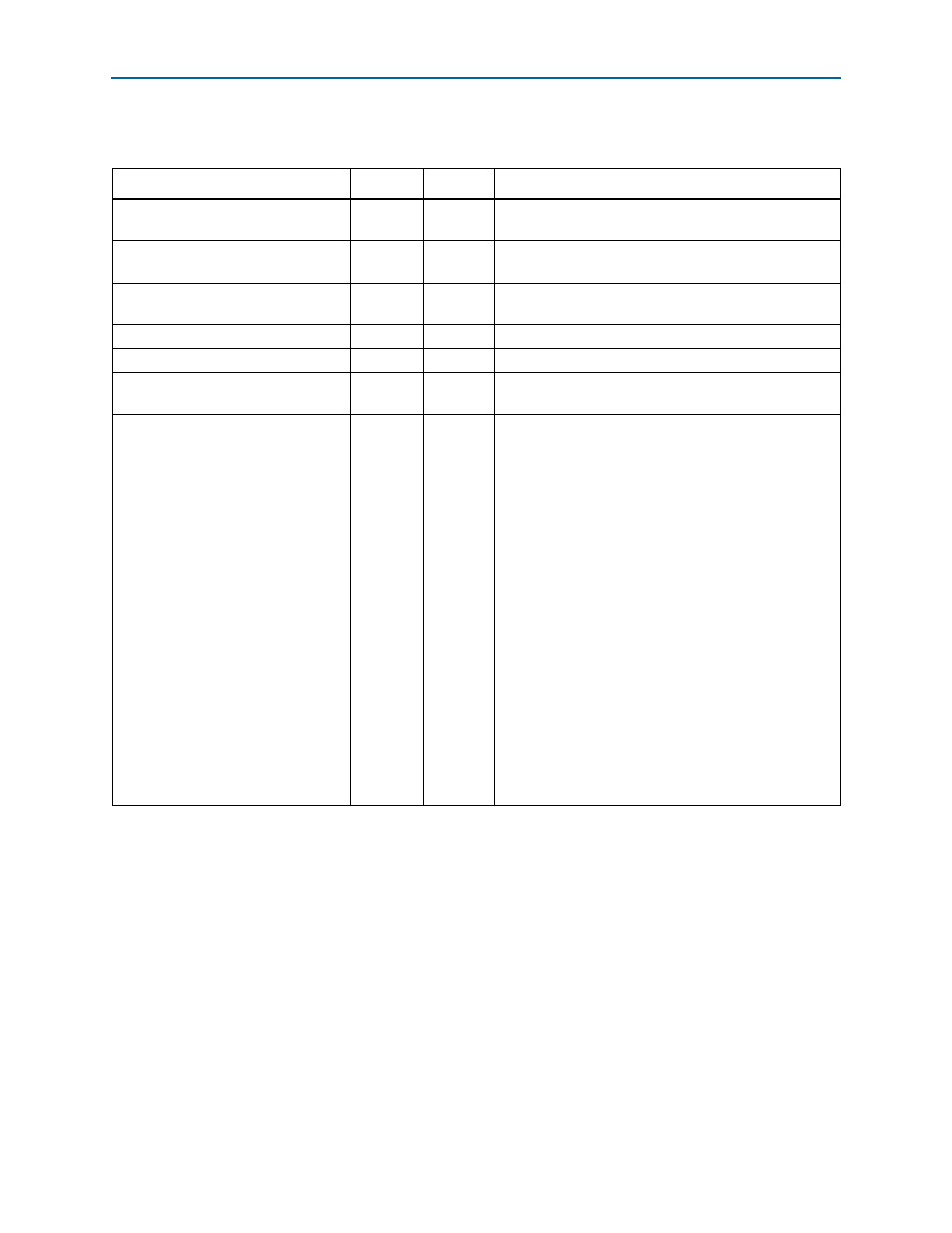

Table 9–3. Avalon-ST Receive Signals

Signal

Direction

Width

Description

avalon_st_rx_startofpacket

Output

1

When asserted, this signal indicates the beginning of the

receive packet.

avalon_st_rx_endofpacket

Output

1

When asserted, this signal indicates the end of the receive

packet.

avalon_st_rx_valid

Output

1

When asserted, this signal qualifies the receive data on

the avalon_st_rx_data bus.

avalon_st_rx_ready

Input

1

Assert this signal when the client is ready to accept data.

avalon_st_rx_data[]

Output

64

Carries the receive data to the client.

avalon_st_rx_empty[]

Output

3

Contains the number of bytes that are empty (not used)

during cycles that contain the end of a packet.

avalon_st_rx_error[]

Output

6

When set to 1, the respective bits in this signal indicate an

error type in the receive frame:

■

Bit 0: PHY error—Indicates PHY error regardless of

the speed you configure.

■

Bit 1: CRC error—The calculated CRC value differs

from the received CRC.

■

Bit 2: Undersized frame—The frame size is less than

64 bytes.

■

Bit 3: Oversized frame—The frame size is more than

MAX_FRAME_SIZE

.

■

Bit 4: Payload length error—The actual frame payload

length differs from the length/type field.

■

Bit 5: Overflow error—The FIFO buffer is full while it is

receiving signal from the MAC causing truncated

receive frame.

The IP core presents the error type on this bus in the

same clock cycle it asserts

avalon_st_rx_endofpacket

and

avalon_st_rx_valid

.