Additional information, Document revision history – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 171

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

Additional Information

This chapter provides additional information about the document and Altera.

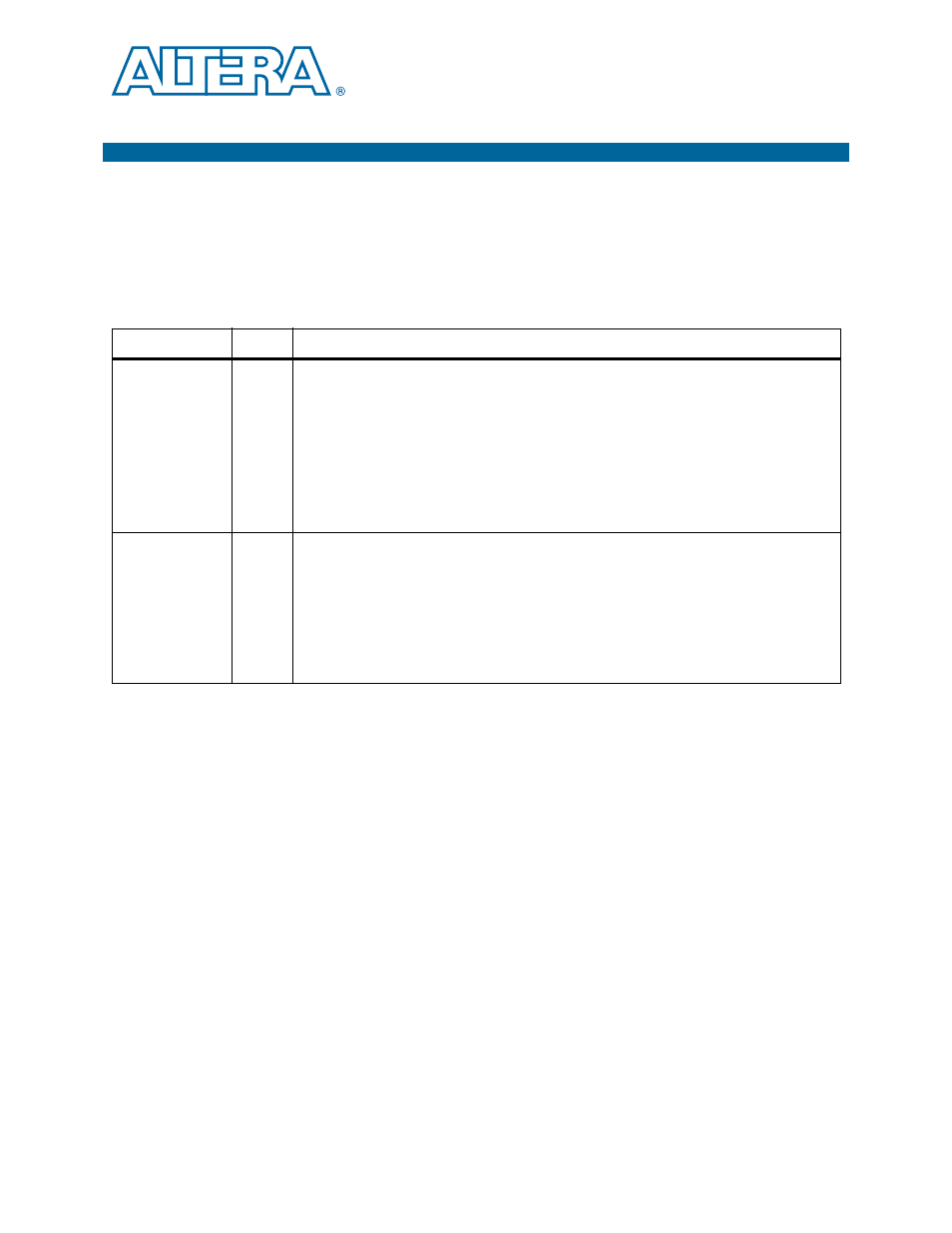

Document Revision History

The following table shows the revision history for this document.

Date

Version

Changes

February 2014

3.3

■

Removed information about Arria GX, HardCopy IV GX, and Stratix II GX devices. Altera

no longer supports these devices.

■

Removed chapters about 1G/10GbE MAC and 10M-10GbE MAC with IEEE 1588v2 design

examples.

■

Updated

with 1G/10Gbps Ethernet PHY support.

■

Edited information for the avalon_st_rxstatus_error register. The error status is no

longer invalid when CRC and/or padding removal is enabled.

■

Added clock information in

“Pause Frame Transmission” on page 7–16

May 2013

3.2.1

■

Added Cyclone V performance and resource utilization data for 10GbE MAC in

and

.

■

Edited the FWD_PFC reset value in

.

■

Edited the PMA analog and digital delay information in

and

.

■

Renamed tx_ingress_timestamp_valid to

tx_etstamp_ins_ctrl_residence_time_update

.