Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 101

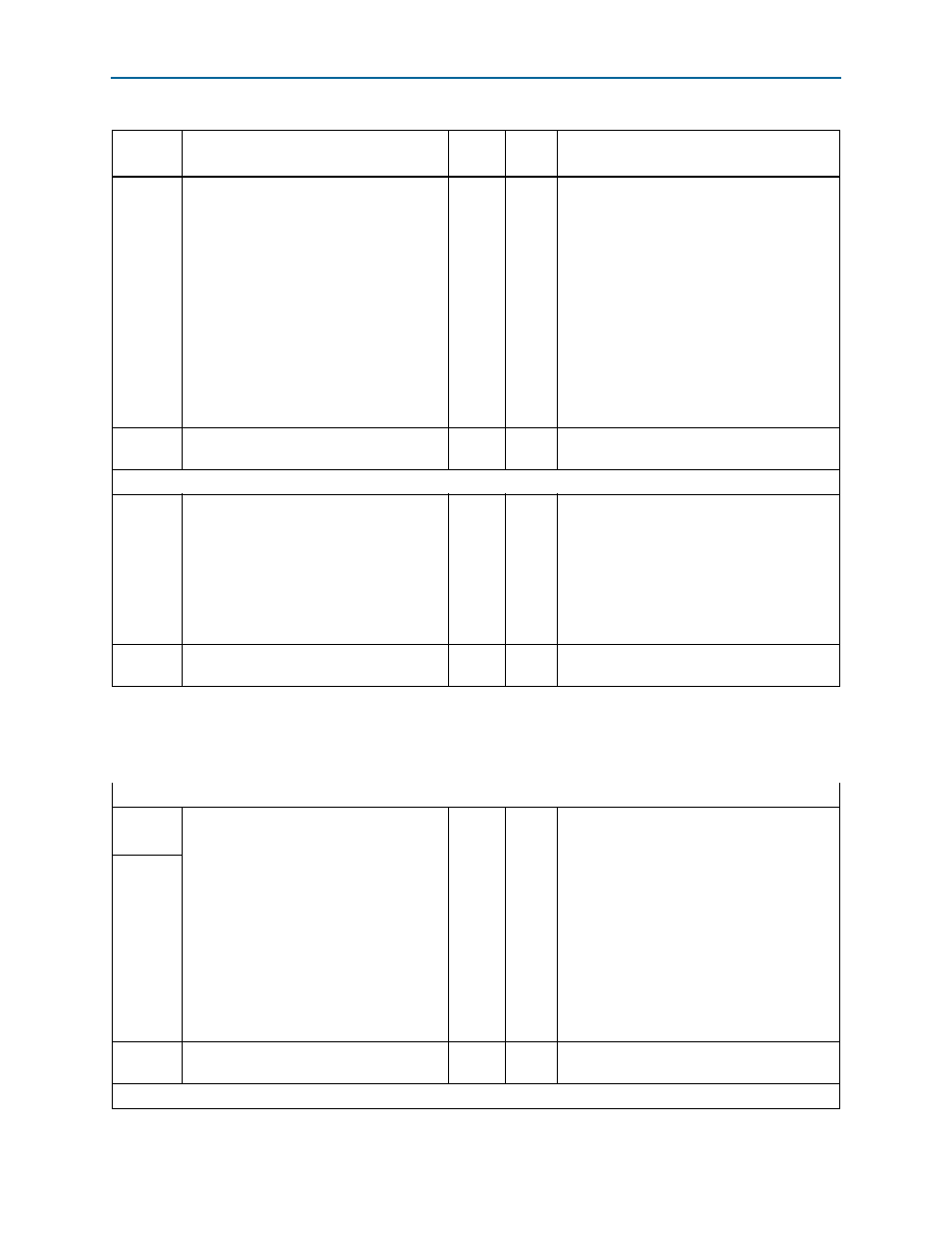

Chapter 8: Registers

8–7

MAC Registers

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

0x1040

tx_padins_control

RW

0x1

■

Bit 0 indicates padding bytes insertion.

0—No effect on transmit frames.The client

must ensure that the length of the data

frame meets the minimum length as

required by the IEEE 802.3 specifications.

1—Inserts padding bytes into transmit

frames until the frame length reaches 60

bytes. To achieve the minimum 64 bytes,

ensure that the CRC field is inserted (refer

to tx_crcins_control).

■

Bits 1 to 31 are reserved.

■

You must enable CRC insertion when you

enable padding bytes insertion.

0x1041 –

0x107F

Reserved

—

—

Reserved for future use.

TX CRC Inserter (0x1080:0x10BF)

0x1080

tx_crcins_control

RW

0x3

CRC insertion.

■

Bit 0—Always set this bit to 1.

■

Bit 1 configures CRC insertion.

0—Disables CRC insertion.

1—Computes CRC and inserts it into

transmit frames.

■

Bits 2 to 31 are reserved.

0x1081 –

0x10BF

Reserved

—

—

Reserved for future use.

TX Packet Underflow (0x10C0:0x10FF)

0x10C0

tx_pktunderflow_error

RO

0x0

36-bit error counter that collects the number

of transmit frames that are truncated when

FIFO buffer underflow persists.

■

The first 32 bits occupy the register at

offset 0x10C0.

■

The last 4 bits occupy the first four bits of

the register at offset 0x10C1.

Bits 4 to 31 are reserved.

The counter will be cleared when the last 4 bits

have been read. If only the first 32 bits are

read, the counter will not be cleared.

0x10C1

0x10C2 –

0x10FF

Reserved

—

—

Reserved for future use.

TX Preamble Control (0x1100:0x113F)

Table 8–2. MAC Registers (Part 6 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description