Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 28

3–10

Chapter 3: 10GbE MAC Design Examples

10GbE Testbenches

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

describes the files that implement the testbench.

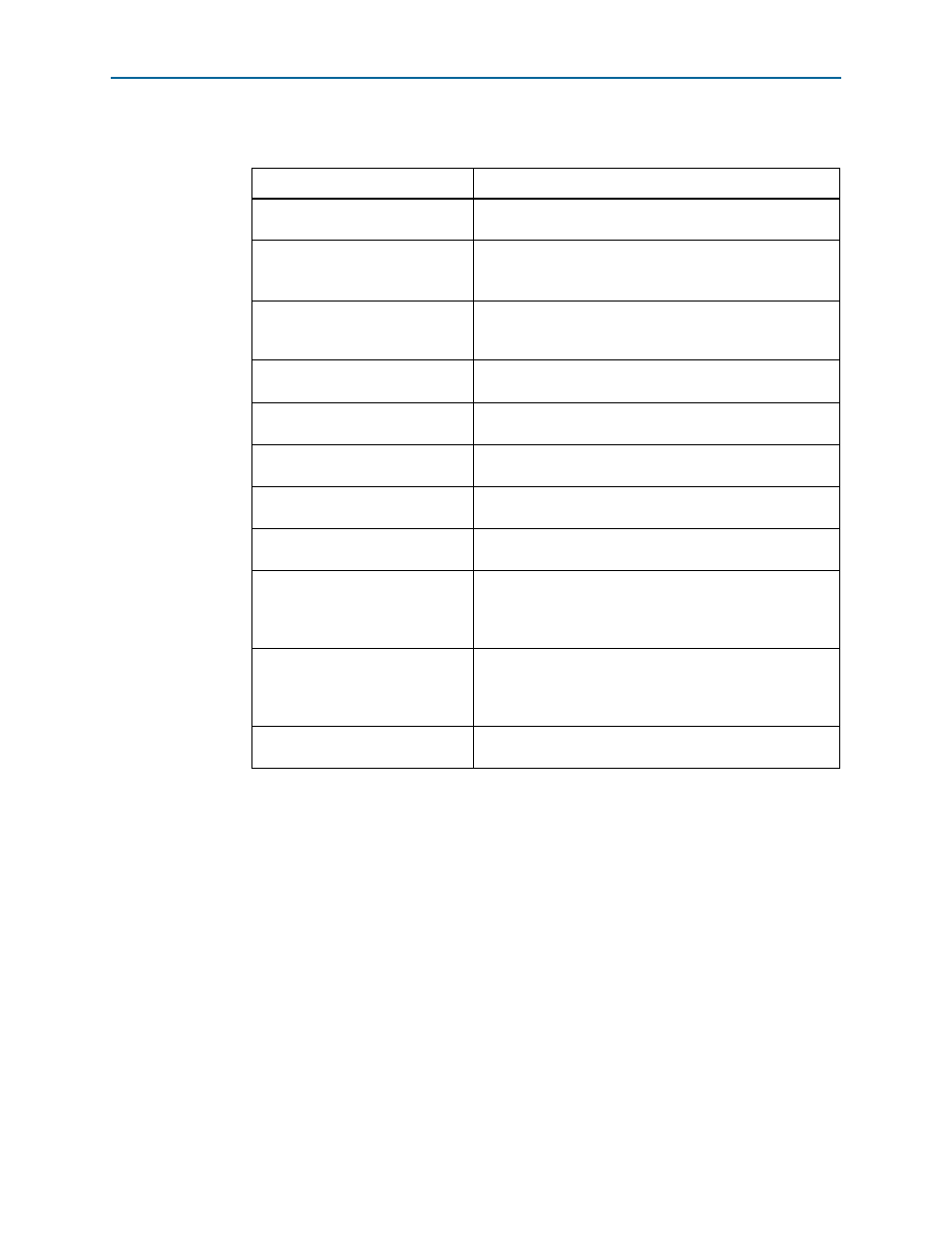

Table 3–5. Testbench Files

File Name

Description

avalon_bfm_wrapper.sv

A wrapper for the Avalon BFMs that the avalon_driver.sv file

uses.

avalon_driver.sv

A SystemVerilog HDL driver that utilizes the BFMs to exercise

the transmit and receive path, and access the Avalon-MM

interface.

avalon_if_params_pkg.sv

A SystemVerilog HDL testbench that contains parameters to

configure the BFMs. Because the configuration is specific to

the DUT, you must not change the contents of this file.

avalon_st_eth_packet_monitor.sv

A SystemVerilog HDL testbench that monitors the Avalon-ST

transmit and receive interfaces.

eth_mac_frame.sv

A SystemVerilog HDL class that defines the Ethernet frames.

The avalon_driver.sv file uses this class.

eth_register_map_params_pkg.sv

A SystemVerilog HDL package that maps addresses to the

Avalon-MM control registers.

tb_run.tcl

A Tcl script that starts a simulation session in the ModelSim

simulation software. Not applicable for Stratix V design.

tb_run_sv.tcl

A Tcl script that starts a simulation session in the ModelSim

simulation software for Stratix V design only.

tb.sv

The top-level testbench file. This file includes the customized

10GbE MAC which is the device under test (DUT), a client

packet generator, and a client packet monitor along with

other logic blocks. Not applicable for Stratix V design.

tb_sv.sv

The top-level testbench file for Stratix V design only. This file

includes the customized 10GbE MAC which is the device

under test (DUT), a client packet generator, and a client

packet monitor along with other logic blocks.

wave.do

A signal tracing macro script to be used with the ModelSim

simulation software to display testbench signals.