D.4. tod synchronizer signals, D.4.1. common clock and reset signals, D.4.2. interface signals – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 169

D–4

Appendix D: ToD Synchronizer

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

D.4. ToD Synchronizer Signals

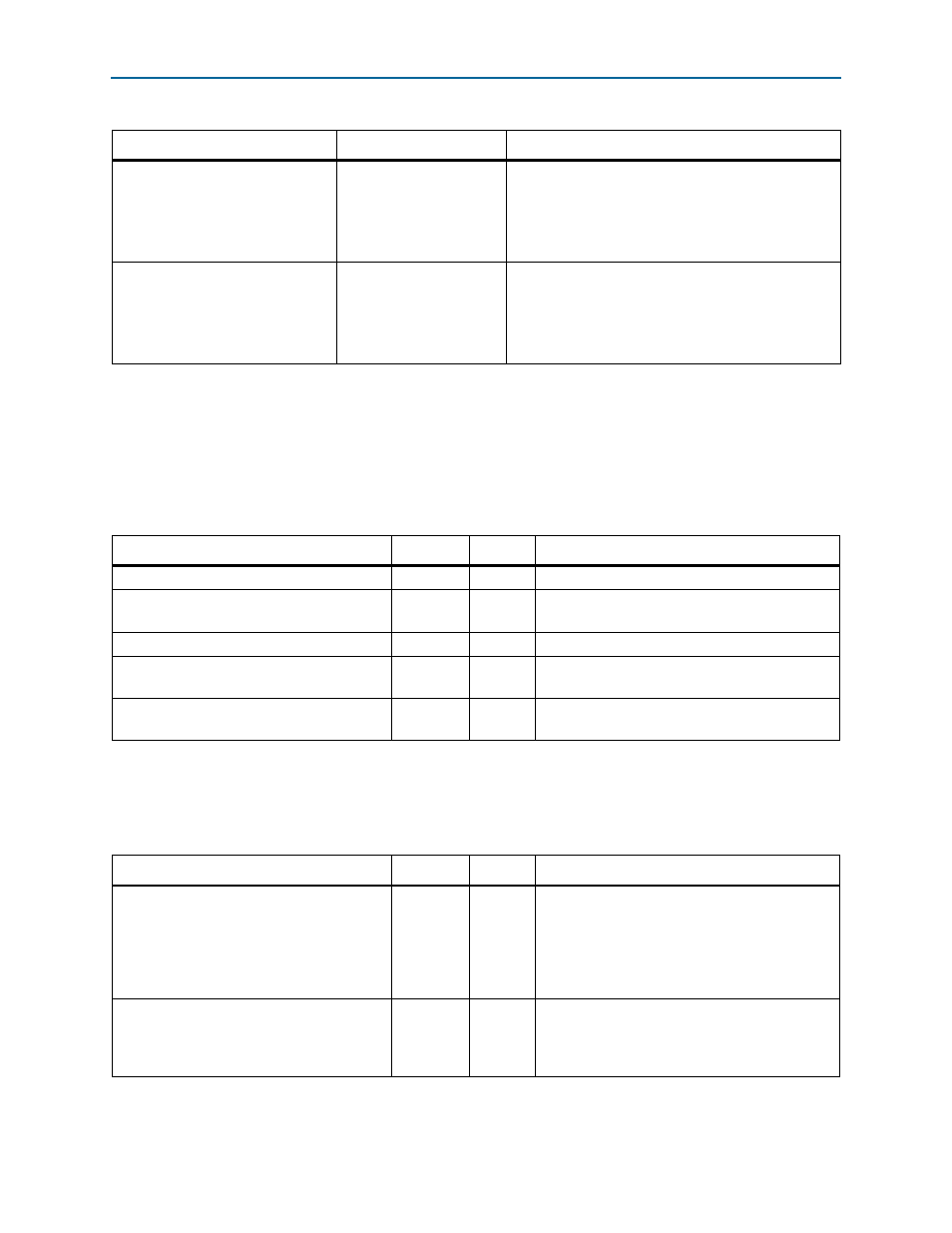

D.4.1. Common Clock and Reset Signals

describes the common clock and reset signals for the ToD Synchronizer.

D.4.2. Interface Signals

lists the interface signals for the ToD Synchronizer.

PERIOD_NSEC

Between 0 and 4’hF

A 4-bit value that defines the reset value for a

nanosecond of period.

The default value is 4'h6 to capture 6.4ns for

156.25MHz frequency. For 125MHz frequency (1G), set

this parameter to 4'h8.

PERIOD_FNSEC

Between 0 and 16’hFFFF

A 4-bit value that defines the reset value for a fractional

nanosecond of period.

The default value is 16'h6666 to capture 0.4ns of 6.4ns

for 156.25MHz frequency. For 125MHz frequency (1G),

set this parameter to 16'h0.

Table D–2. ToD Synchronizer Configuration Parameters

Name

Value

Description

Table D–2. Clock and Reset Signals for the ToD Synchronizer

Signal

Direction

Width

Description

clk_master

Input

1

Clock from master ToD domain.

reset_master

Input

1

Reset signal that is synchronized to the master

ToD clock domain.

clk_slave

Input

1

Clock from slave ToD domain.

reset_slave

Input

1

Reset signal that is synchronized to the slave ToD

clock domain.

clk_sampling

Input

1

Sampling clock to measure the latency across the

ToD Synchronizer.

Table D–3. Interface Signals for the ToD Synchronizer (Part 1 of 2)

Signal

Direction

Width

Description

start_tod_sync

Input

1

Assert this signal to start the ToD synchronization

process. When this signal is asserted, the

synchronization process continues and the time of

day from the master ToD clock domain will be

repeatedly synchronized with the slave ToD clock

domain.

tod_master_data

Input

1

This signal carries the 64-bit or 96-bit format data

for the time of day from the master ToD. The width

of this signal is determined by the TOD_MODE

parameter.