Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 59

5–14

Chapter 5: 1G/10GbE MAC Design Example

1G/10GbE Design Example Compilation

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

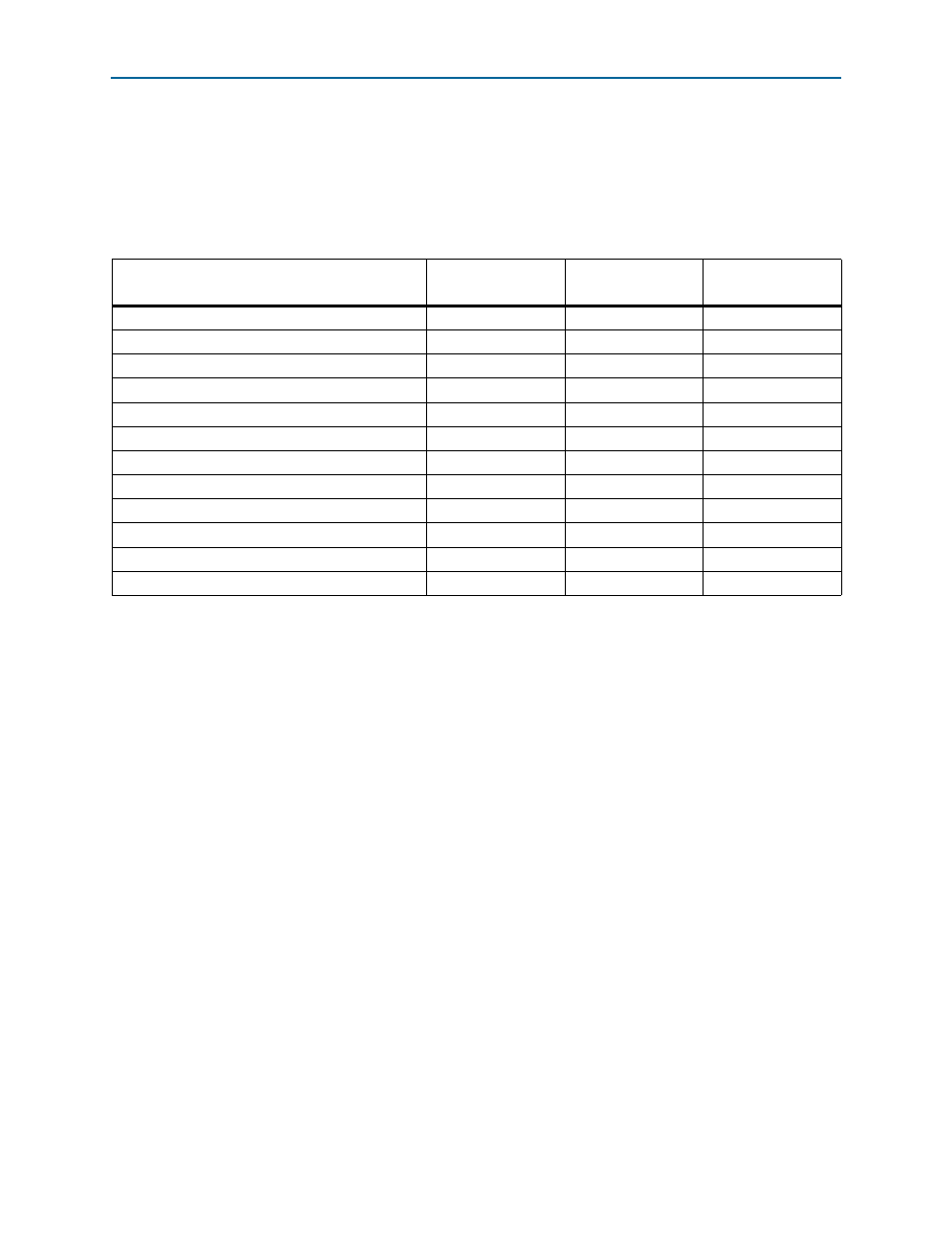

5.6.2. 1G/10GbE Design Performance and Resource Utilization

Table 5–5

provides the estimated performance and resource utilization of the

1G/10GbE design example obtained by compiling the design with the Quartus II

software targeting the Stratix V GX (EP5SGXEA7N2F40C2) device with speed grade

–2.

Table 5–5. Stratix V Performance and Resource Utilization

Components

ALM Needed

ALM in Final

Placement

Memory Block

1G/10GbE MAC Channel 0

3,272

3,900

9

1G/10GbE MAC Channel 1

3,302

3,891

9

10GBASE-KR Channel 0

547

685

1

10GBASE-KR Channel 1

547

690

1

Reconfiguration Bundle

1,644

1,940

8

JTAG Master

341

424

1

RX FIFO (Avalon-ST Single-Clock FIFO) Channel 0

142

172

2

TX FIFO (Avalon-ST Single-Clock FIFO) Channel 0

140

180

2

RX FIFO (Avalon-ST Single-Clock FIFO) Channel 1

138

176

2

TX FIFO (Avalon-ST Single-Clock FIFO) Channel 1

139

176

2

Other Components

2,628

3,123

8

Total Resource Utilization

12,840

15,357

45