Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 129

9–10

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

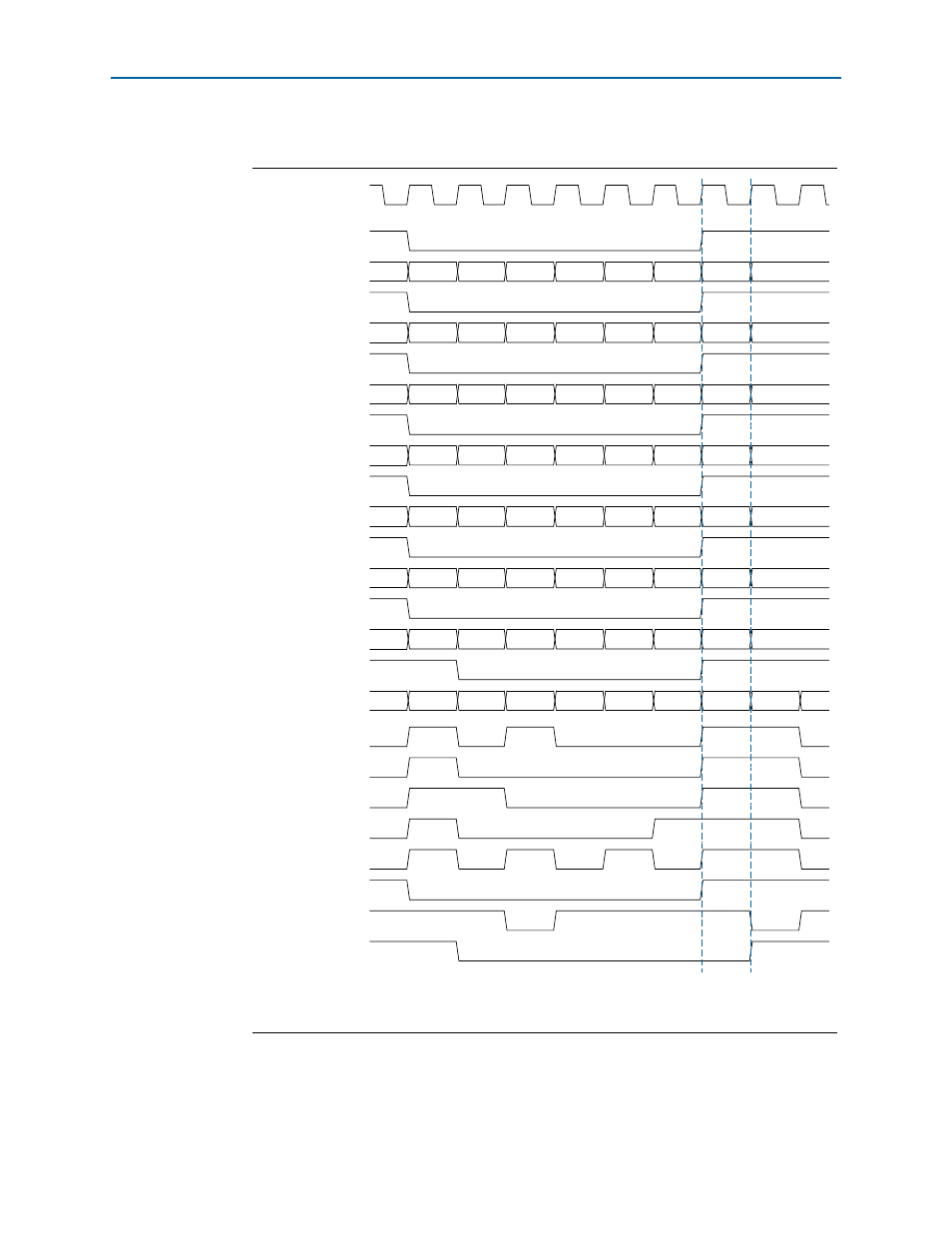

Figure 9–8

shows the timing for the SDR XGMII RX interface when an error occurs.

Figure 9–8. SDR XGMII RX Interface with Error

Note to

Figure 9–8

:

(1) The xgmii_rx_data[7:0] bus is expanded to show the behavior of each signal when an error occurs.

rx_clk_clk

xgmii_rx_data [71]

xgmii_rx_data [70:63]

xgmii_rx_data [62]

xgmii_rx_data [61:54]

xgmii_rx_data [53]

xgmii_rx_data [52:45]

xgmii_rx_data [44]

xgmii_rx_data [43:36]

xgmii_rx_data [35]

xgmii_rx_data [34:27]

xgmii_rx_data [26]

xgmii_rx_data [25:18]

xgmii_rx_data [17]

xgmii_rx_data [16:9]

xgmii_rx_data [8]

xgmii_rx_data [7:0]

xgmii_rx_data [7]

xgmii_rx_data [6]

xgmii_rx_data [5]

xgmii_rx_data [4]

xgmii_rx_data [3]

xgmii_rx_data [2]

xgmii_rx_data [1]

xgmii_rx_data [0]

D5

CC

01

09

11

19

FE

55

EE

00

08

10

18

FE

55

CC

1E

07

0F

17

FE

55

AA

00

06

0E

16

FE

55

88

EE

05

0D

15

FE

55

66

AA

04

0C

14

FE

55

44

CC

03

0B

13

FE

FB

22

88

02

0A

12

FE

FD

(1)