Rx_frame_control register, Rx_frame_control register –16, Rx_frame_control register” on – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 110

8–16

Chapter 8: Registers

MAC Registers

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

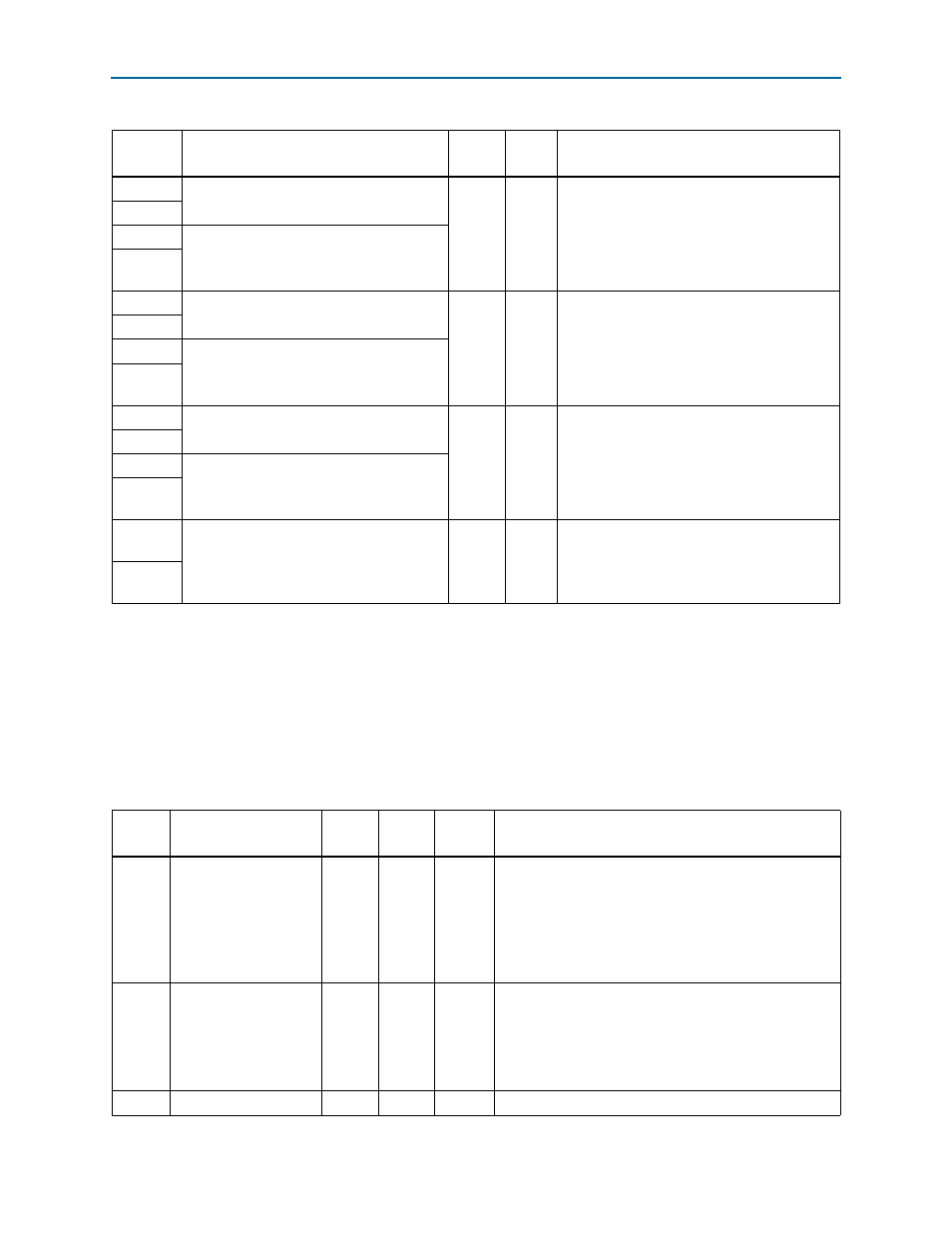

8.1.1. Rx_frame_control Register

Table 8–3

describes the function of each field in the

rx_frame_control

register.

0x0C38

rx_stats_multicastMAC CtrlFrames

RO

0x0

■

Bit 0—The number of valid multicast

control frames received or transmitted.

■

36-bit width register:

■

0x0C38 and 0x0C39 = bits [31:0]

■

0x1C38 and 0x1C39 = bits [35:32]

0x0C39

0x1C38

tx_stats_multicastMAC CtrlFrames

0x1C39

0x0C3A

rx_stats_broadcastMAC CtrlFrames

RO

0x0

■

Bit 0—The number of valid broadcast

control frames received or transmitted.

■

36-bit width register:

■

0x0C3A and 0x0C3B = bits [31:0]

■

0x1C3A and 0x1C3B = bits [35:32]

0x0C3B

0x1C3A

tx_stats_broadcastMAC CtrlFrames

0x1C3B

0x0C3C

rx_stats_PFCMACCtrlFrames

RO

0x0

■

Bit 0—The number of valid PFC frames

received or transmitted.

■

36-bit width register:

■

0x0C3C and 0x0C3D = bits [31:0]

■

0x1C3C and 0x1C3D = bits [35:32]

0x0C3D

0x1C3C

tx_stats_PFCMACCtrlFrames

0x1C3D

0x0C3E –

0x0FFF

Reserved

—

—

Reserved for future use.

0x1C3E –

0x1FFF

Notes to

Table 8–2

:

(1) When you read the statistic counters, read the LSB before reading the MSB. For example, when you read rx_stats_PFCMACCtrlFrames, read

the register offset 0x0C3C before reading the register offset 0x0C3D.

(2) If you set the statistics counters to memory-based implementation, the number of undersized frames received or transmitted is not incremented

for this register. This is due to the limited processing time when undersized frames are received or transmitted.

Table 8–2. MAC Registers (Part 15 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description

Table 8–3. Rx_frame_control Register (Part 1 of 2)

Bit

Field Name

Width

Access

Reset

Value

Description

0

EN_ALLUCAST

1

RW

0x1

0—Drops unicast receive frames using the primary MAC

addresses.

1—Accepts all unicast receive frames.

Setting this register and the EN_ALLMCAST register to 1,

enables the MAC to go on promiscuous (transparent)

mode.

1

EN_ALLMCAST

1

RW

0x1

0—Drops all multicast frames.

1—Accepts all multicast frames.

Setting this register and the EN_ALLUCAST register to 1,

enables the MAC to go on promiscuous (transparent)

mode.

2

Reserved

1

—

—

Reserved for future use.