Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 48

Chapter 5: 1G/10GbE MAC Design Example

5–3

1G/10GbE Design Example Components

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

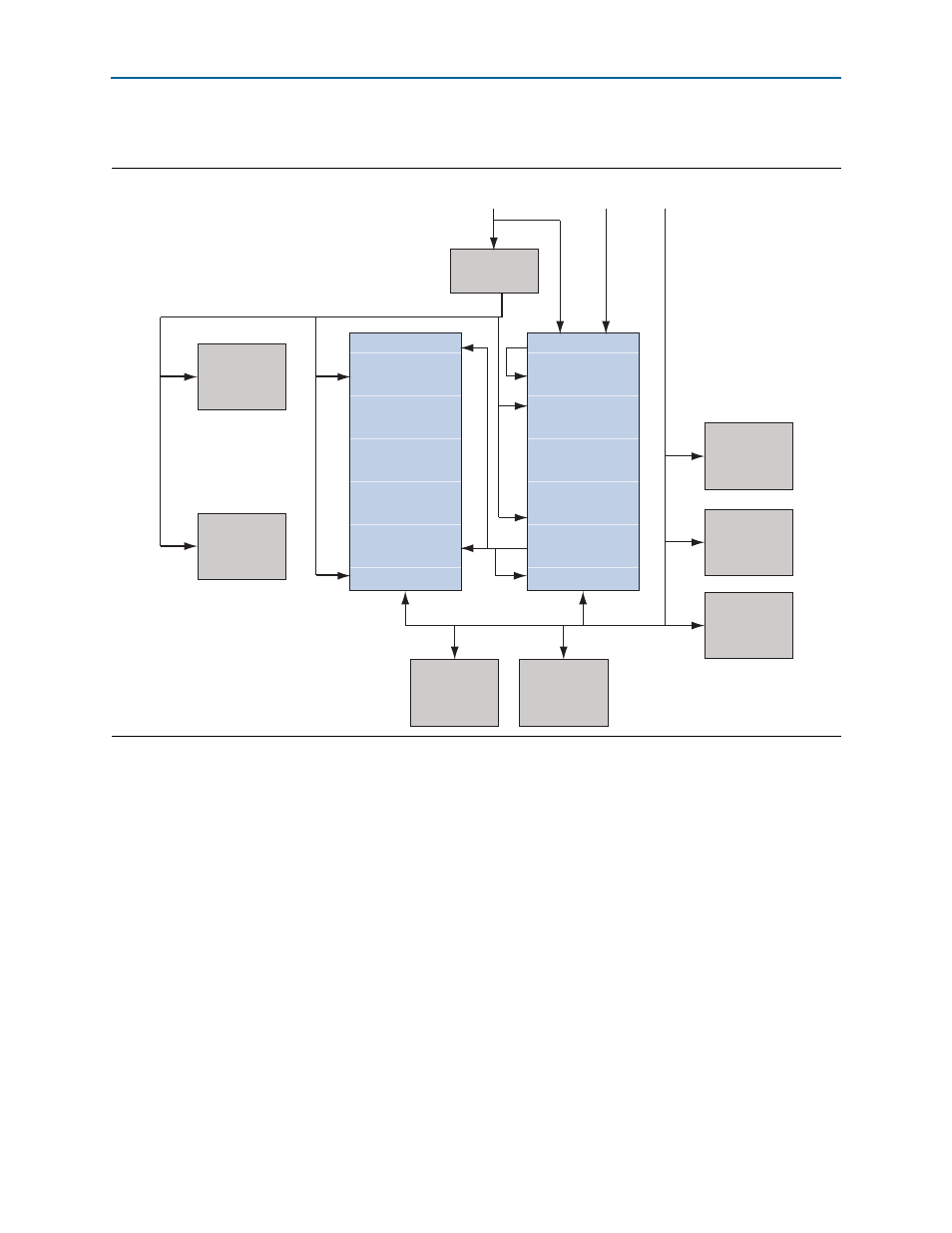

shows the clocking scheme for the design example.

The 1G/10GbE design example comprises the following components:

■

1G/10GbE Ethernet MAC—the MAC IP core with default settings. This IP core

includes memory-based statistics counters.

■

Backplane Ethernet 10GBASE-KR PHY—the PHY IP core operating as either

1000BASE-X PHY or 10GBASE-R PHY.

■

Reconfiguration Bundle—comprises the reconfiguration controller that switches

the speed between 1 Gbps and 10 Gbps, and the management ROM that stores

MIF information for 1/10GbE PHY or HSSI or hard PCS. This block arbitrates the

access to the reconfiguration controller and requests the reconfiguration controller

to start streaming MIF information.

■

Single-Clock FIFO—Avalon-ST Single-Clock RX and TX FIFO cores that buffer

receive and transmit data between the MAC and the client. These FIFO buffers are

64 bits wide and 2048 bits deep. The Single-Clock FIFO operates in store and

forward mode, and you can configure it to provide packet-based flushing when an

error occurs.

Figure 5–2. 1G/10GbE Design Example Clocking Scheme

Single-Clock

FIFO

Single-Clock

FIFO

PLL

JTAG to Avalon

Master Bridge

Pipeline

Bridge

10GBASE-KR

PHY

1G/10GbE

MAC

Configure

Reconfig

gmii_rx_clk

gmii_tx_clk

rx_coreclkin_1g

rx_clkout_1g

xgmii_rx_clk

tx_clkout_1g

xgmii_tx_clk

tx_coreclkin_1g

rx_clk

ref clk

322.265625

ref clk

125

mm clk

100

tx_clk

125 Mhz

125 Mhz

156.25 Mhz

Reconfiguration

Bundle

PHY IP

Reset Controller