10gbe with ieee 1588v2 design example components – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 40

4–2

Chapter 4: 10GbE MAC with IEEE1588v2 Design Example

10GbE with IEEE 1588v2 Design Example Components

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

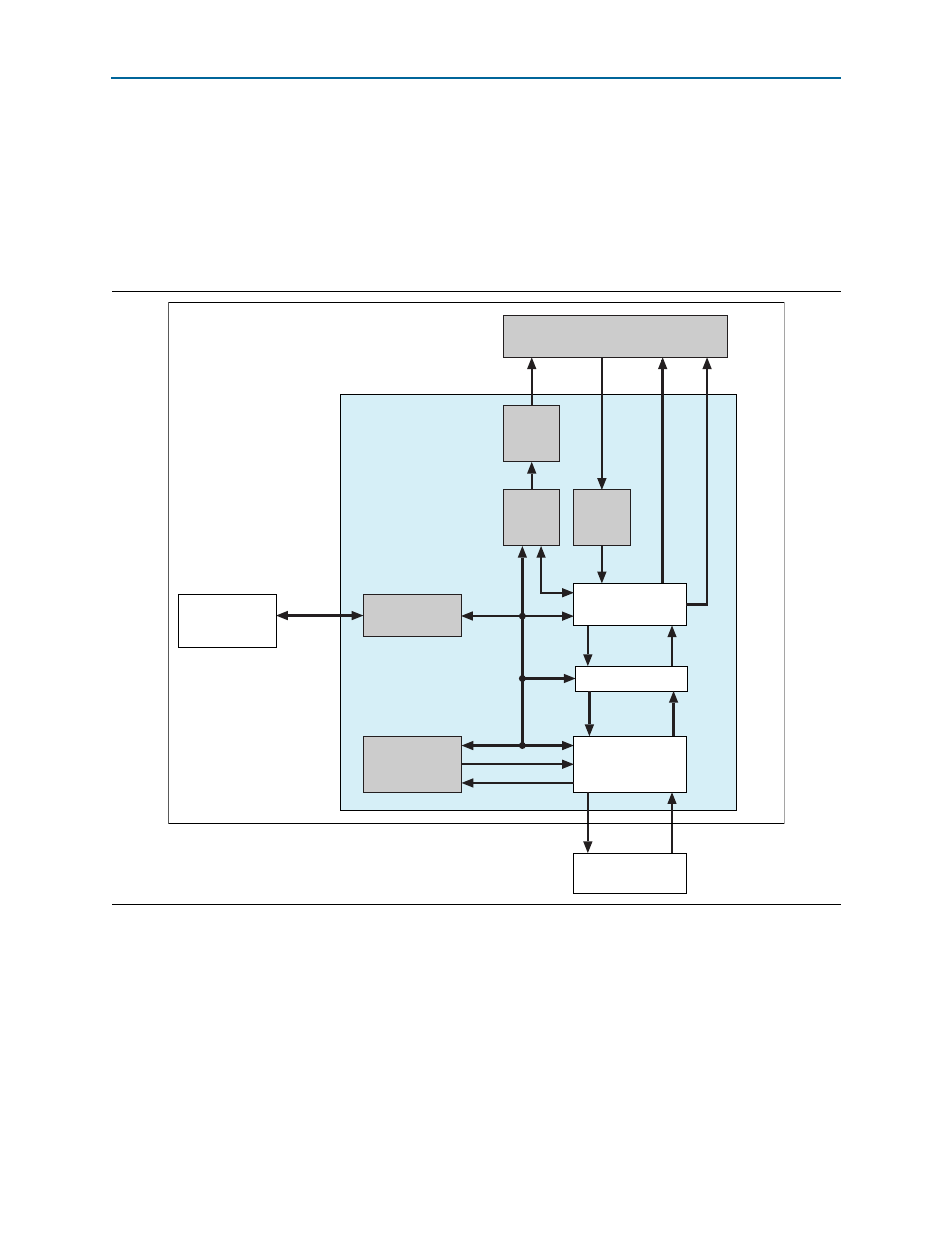

4.2. 10GbE with IEEE 1588v2 Design Example Components

You can use the 10GbE MAC IP core design example to simulate a complete 10GbE

with IEEE 1588v2 design in a simulator. You can compile the design example using

the Quartus II software and program the targeted Altera device after a successful

compilation.

shows the block diagram of the 10GbE with IEEE 1588v2 design example.

Figure 4–1. 10GbE with IEEE 1588v2 Design Example Block Diagram

Ethernet

Packet

Classifier

Pulse Per

Second

Module

Time of

Day

Clock

Time of Day

10GbE MAC

Avalon MM Master

Translator

Client Application

(Configuration,

Status & Statistics)

Transceiver

Reconfiguration

Controller

10GBASE-R PHY

External PHY

10GBASE-R

72-Bit SDR

XGMII

64-Bit

Avalon ST

Time

of Day

32-Bit

Avalon MM

Reconfiguration

32-Bit

Avalon MM

64-Bit

Avalon ST

Pulse Per

Second

Timestamp &

Fingerprint

Client Application

Altera FPGA

Design Example

Ethernet Loopback

72-Bit SDR

XGMII