Mac registers, Mac registers –2, Refer to – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 96

8–2

Chapter 8: Registers

MAC Registers

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

1

If you instantiate the IP core using the MegaWizard Plug-in Manager flow, use double

word (dword) addressing to access the register spaces. Convert the byte offsets to

dword offsets by dividing the byte offsets by 4. For example,

■

rx_padcrc_control

byte offset = 0x100

■

rx_padcrc_control

word offset = 0x100 ÷ 4 = 0x040

1

Do not reconfigure the MAC through the CSR registers when the datapath is not idle,

with the exception of the following registers:

■

tx_transfer_control

■

rx_transfer_control

■

tx_pauseframe_control

■

tx_stats_clr

■

rx_stats_clr

■

rx_pfc_control

■

All IEEE 1588v2 CSR registers

8.1. MAC Registers

Table 8–2

shows the MAC registers.

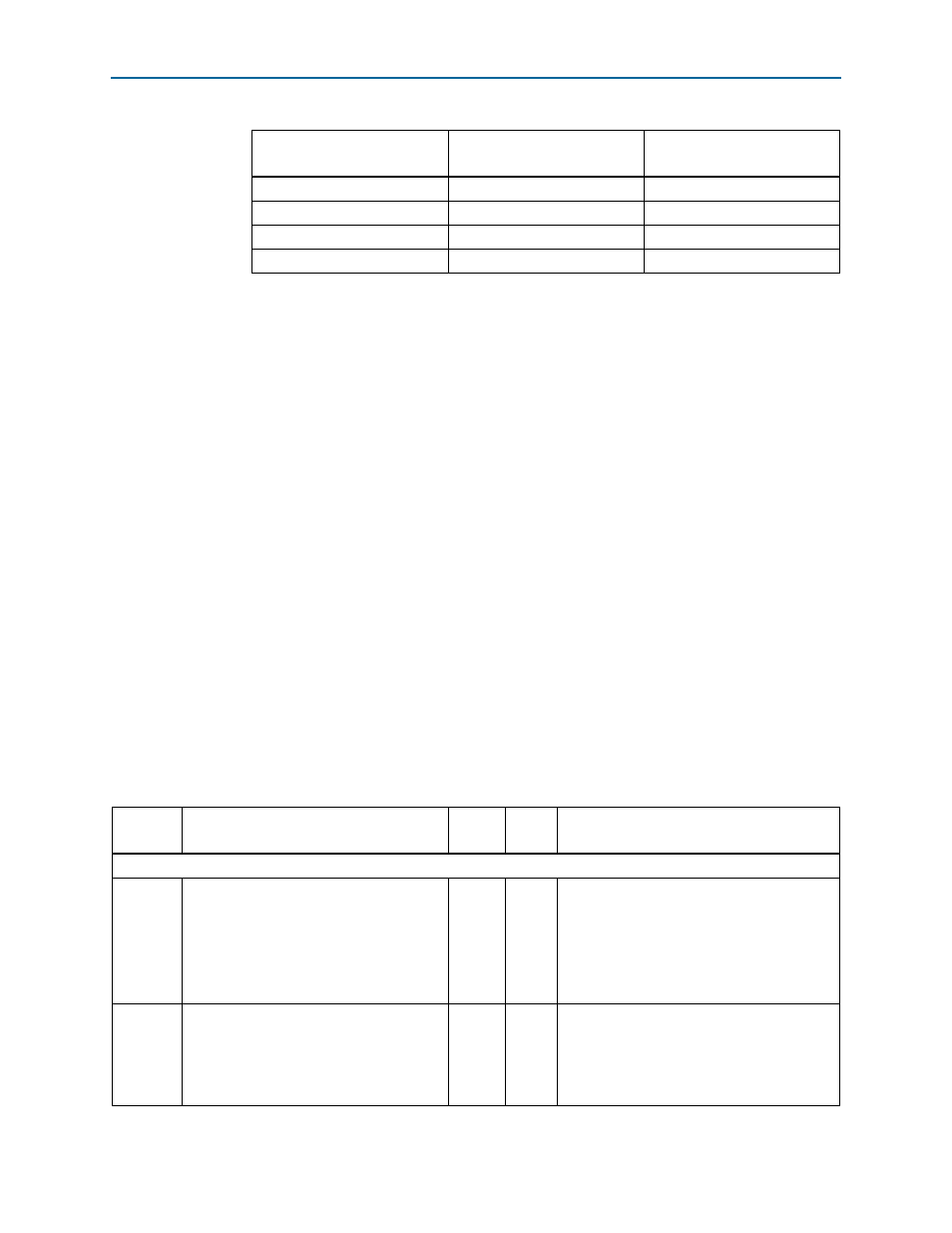

TX PFC Generator

—

0x4600:0x47FF

TX Address Inserter

0x480:0x4FF

0x4800:0x5FFF

TX Frame Decoder

0x500:0x57F

0x6000:0x6FFF

TX Statistics Counters

0x600:0x7FF

0x7000:0x7FFF

Table 8–1. Summary of Register Address Expansion

Component Name

Previous Address Range

(ACDS Version 10.0, 10.1)

New Address Range

(ACDS Version 11.0 Onwards)

Table 8–2. MAC Registers (Part 1 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description

RX Packet Transfer (0x000:0x03F)

0x000

rx_transfer_control

RW

0x0

Receive path enable.

■

Bit 0 configures the receive path.

0—Enables the receive path.

1—Disables the receive path and drops all

receive frames.

■

Bits 1 to 31 are reserved.

0x001

rx_transfer_status

RO

0x0

■

Bit 0 indicates the status of the receive

path.

0—The receive path is enabled.

1—The receive path is disabled.

■

Bits 1 to 31 are reserved.