C.2. packet classifier signals, C.2.1. common clock and reset signals, C.2.2. avalon-st interface signals – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 163

C–2

Appendix C: Packet Classifier

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

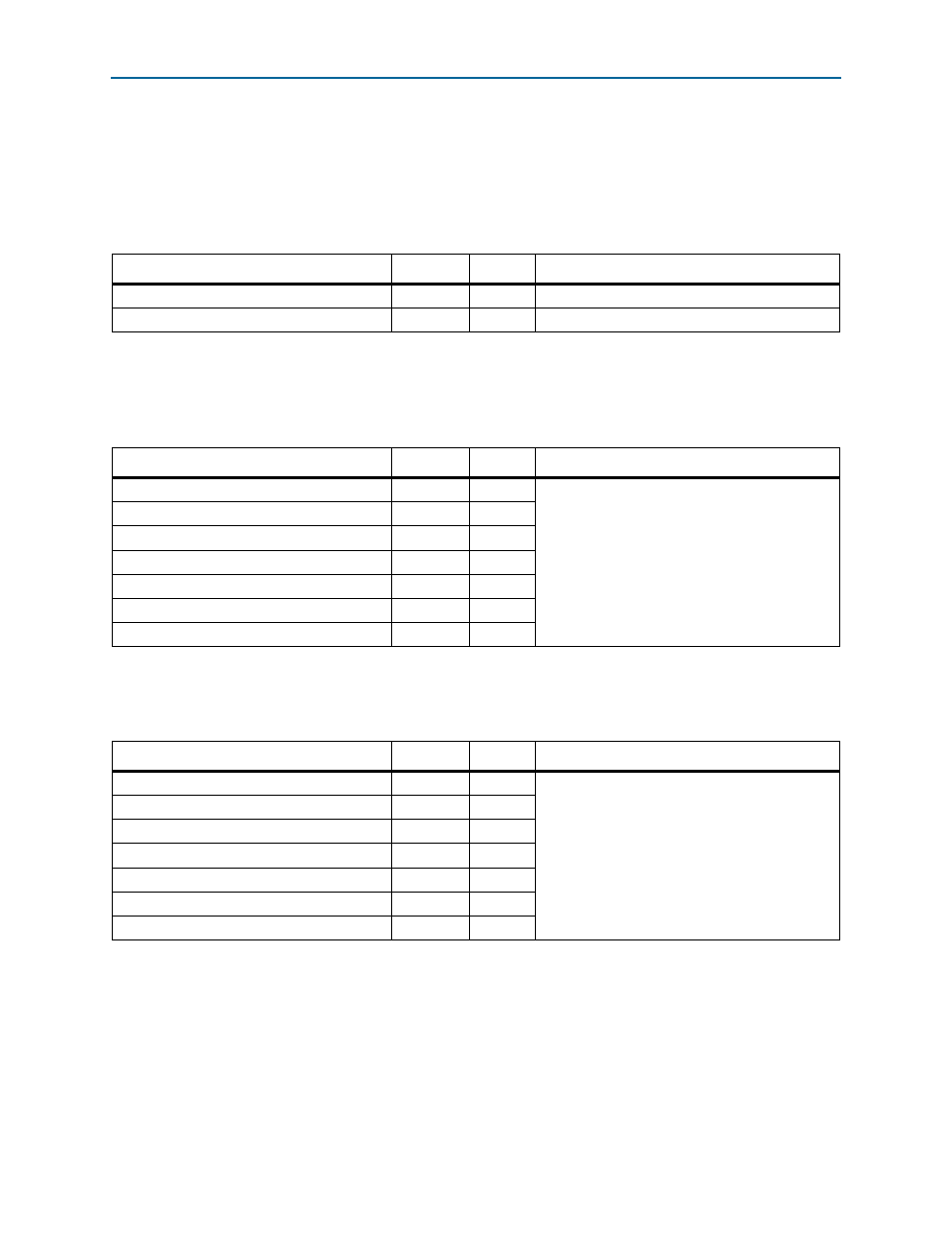

C.2. Packet Classifier Signals

C.2.1. Common Clock and Reset Signals

Table C–1

describes the common clock and reset signals for the Packet Classifier.

C.2.2. Avalon-ST Interface Signals

lists the Avalon-ST DataIn (sink) interface signals for the Packet Classifier.

lists the Avalon-ST DataOut (source) interface signals for the Packet

Classifier.

Table C–1. Clock and Reset Signals for the Packet Classifier

Signal

Direction

Width

Description

clk

Input

1

156.25-MHz register access reference clock.

reset

Input

1

Assert this signal to reset the clock.

Table C–2. Avalon-ST DataIn Interface Signals for the Packet Classifier

Signal

Direction

Width

Description

data_sink_sop

Input

1

The Avalon-ST input frames.

data_sink_eop

Input

1

data_sink_valid

Input

1

data_sink_ready

Output

1

data_sink_data

Input

64

data_sink_empty

Input

3

data_sink_error

Input

1

Table C–3. Avalon-ST DataOut Interface Signals for the Packet Classifier

Signal

Direction

Width

Description

data_src_sop

Input

1

The Avalon-ST output frames.

data_src_eop

Input

1

data_src_valid

Input

1

data_src_ready

Output

1

data_src_data

Input

64

data_src_empty

Input

3

data_src_error

Input

1