Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 98

8–4

Chapter 8: Registers

MAC Registers

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

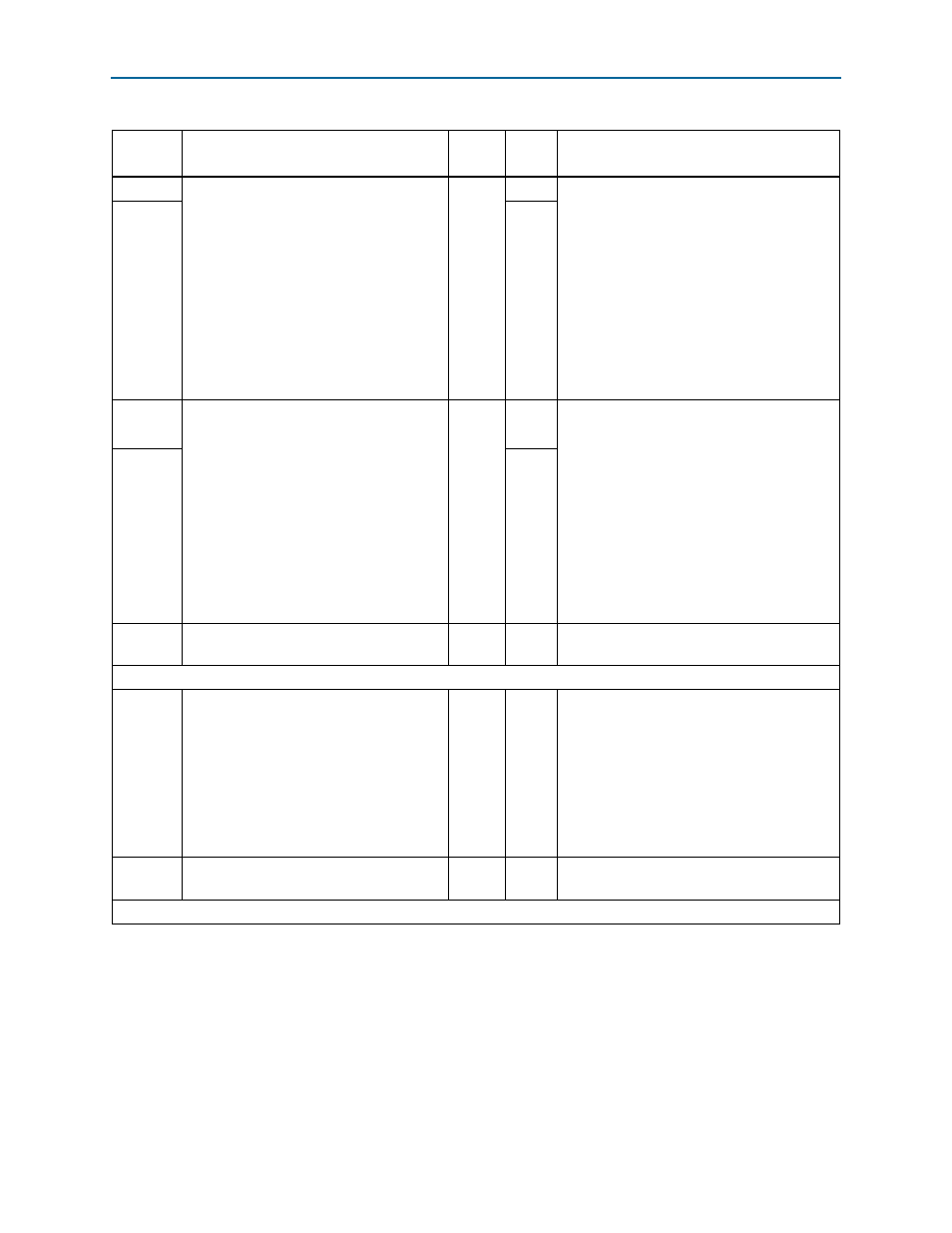

0x0C0

rx_pktovrflow_error

RO

0x0

36-bit error counter that collects the number

of receive frames that are truncated when FIFO

buffer overflow persists:

■

The first 32 bits occupy the register at

offset 0x0C0.

■

The last 4 bits occupy the first four bits of

the register at offset 0x0C1. Bits 4 to 31 are

unused.

The counter will be cleared when the last 4 bits

have been read. If only the first 32 bits are

read, the counter will not be cleared.

0x0C1

0x0

0x0C2

rx_pktovrflow_

etherStatsDropEvents

RO

0x0

36-bit error counter that collects the number

of receive frames that are dropped when FIFO

buffer overflow persists:

■

The first 32 bits occupy the register at

offset 0x0C2.

■

The last 4 bits occupy the first four bits of

the register at offset 0x0C3. Bits 4 to 31 are

unused.

The counter will be cleared when the last 4 bits

have been read. If only the first 32 bits are

read, the counter will not be cleared.

0x0C3

0x0

0x0C4 –

0x0FF

Reserved

—

—

Reserved for future use.

RX Preamble Control (0x100:0x13F)

0x100

rx_lane_decoder_preamble_control

RW

0x0

■

Bit 0 determines whether or not the

client-defined preamble is forwarded to the

client frame.

0—Removes the client-defined preamble

from the receive frame.

1—Forwards the client-defined preamble to

the client.

■

Bits 1 to 31 are reserved.

0x101 –

0x13F

Reserved

—

—

Reserved for future use.

RX Lane Decoder (0x140:0x7FF)

Table 8–2. MAC Registers (Part 3 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description