Correctable error status register – Altera Stratix V Avalon-ST User Manual

Page 101

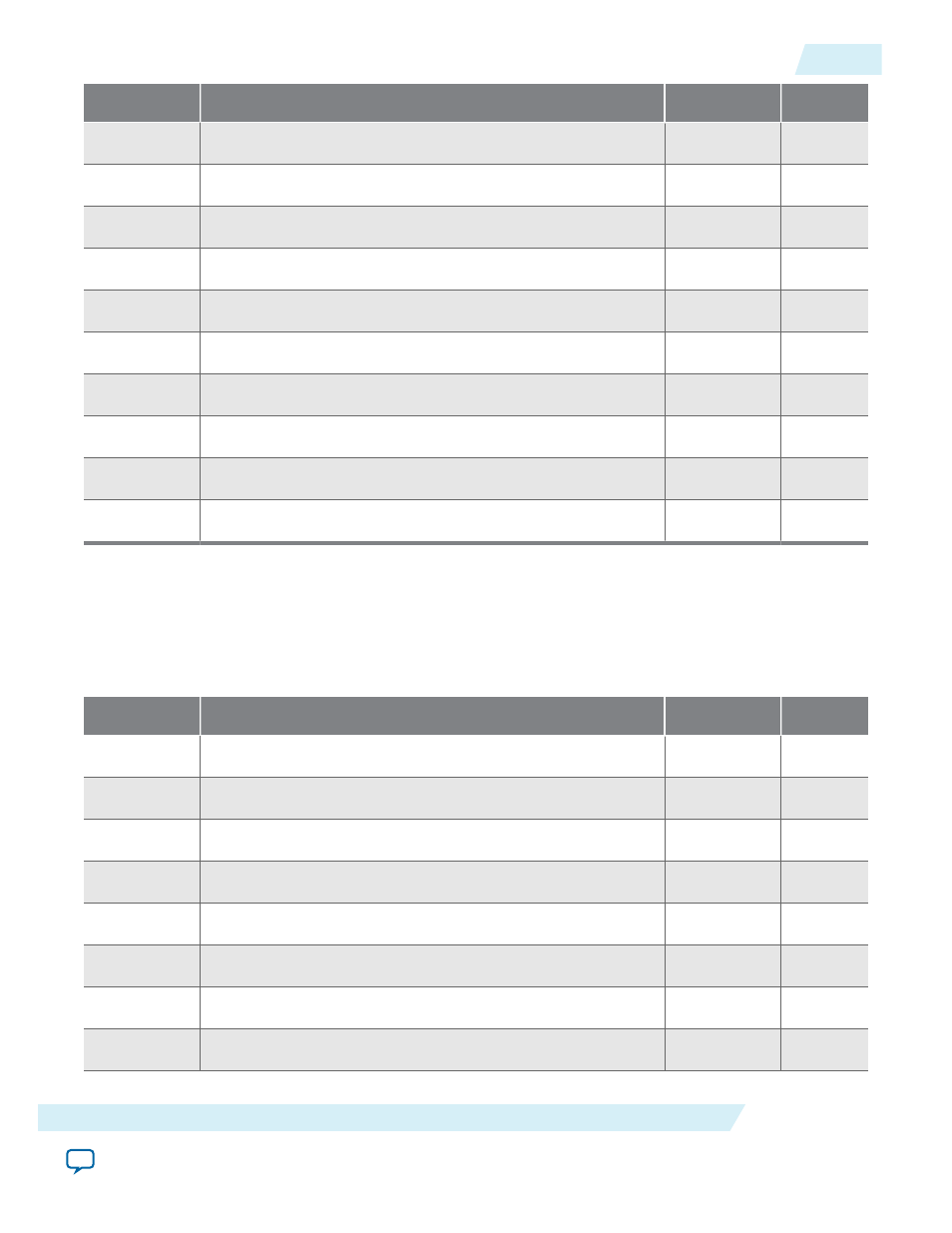

Bits

Register Description

Default Value

Access

[18]

Malformed TLP Received

1

RW

[17]

Receiver Overflow

1

RW

[16]

Unexpected Completion was received

0

RW

[15]

Completer Abort (CA) was transmitted

0

RW

[14]

Completion Timeout

0

RW

[13]

Flow Control protocol error

1

RW

[12]

Poisoned TLP

0

RW

[11:5]

Reserved

0

RO

[4]

Data Link Protocol error

1

RW

[3:0]

Reserved

0

RO

Related Information

Correctable Error Status Register

Table 5-44: Correctable Error Status Register - 0x150 (ARI supported) or (0x110 ARI not supported)

Bits

Register Description

Default Value

Access

[31:14]

Reserved

0

RO

[13]

When set, indicates an Advisory Non-Fatal Error

0

RW1C

[12]

When set, indicates a Replay Timeout

0

RW1C

[11:9]

Reserved

0

RO

[8]

When set, indicates a Replay Number Rollover

0

RW1C

[7]

When set, indicates a Bad DLLP received

0

RW1C

[6]

When set, indicates a Bad TLP received

0

RW1C

[5:1]

Reserved

0

RO

UG-01097_sriov

2014.12.15

Correctable Error Status Register

5-27

Registers

Altera Corporation