Altera Stratix V Avalon-ST User Manual

Page 79

1. A rising edge on

app_intx_req

indicates the assertion of the corresponding legacy interrupt from the

client.

2. In response, the PF drives

Assert_INTx

to activate a legacy interrupt.

3. A falling edge on

app_int_sts_x

indicates the deassertion of the corresponding legacy interrupt from

the client.

4. In response, the PF sends

Deassert_INTx

to deactivate the legacy interrupt.

The

Interrupt Pin

register specifies the interrupt input used to signal interrupts. The PFs may be

configured with separate interrupt pins. Or, both PFs may share a common interrupt pin. You configure

the

Interrupt Pin

register in Qsys.

The

Interrupt Line

register specifies the interrupt controller (IRQ0–IRQ15) input of the in the Root

Port activated by each

Assert_INTx

message. You configure the

Interrupt Line

register in Qsys.

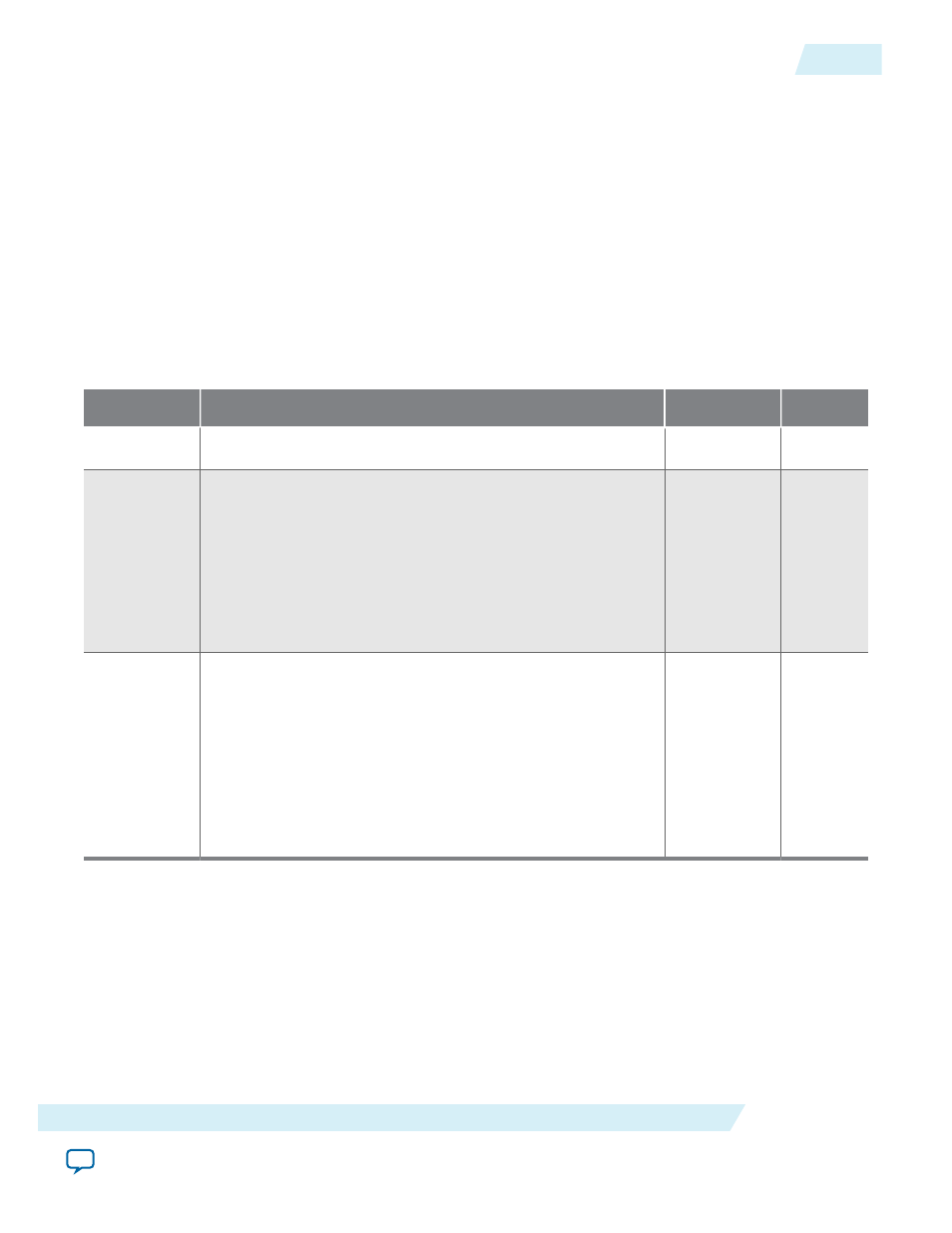

Table 5-3: Interrupt Line and Interrupt Pin Register -0x03C

Bit Location

Description

Default Value

Access

[15:11]

Not implemented

0

RO

[10:8]

Interrupt Pin register. When legacy interrupts are enabled,

specifies the pin this function uses to signal an interrupt . The

following encodings are defined:

• 3'b001: INTA_IN

• 3'b010: INTB_IN

• 3'b011: INTC_IN

• 3'b100: INTD_IN

Specify in Qsys

RO

[7:0]

Interrupt Line register. Identifies the interrupt controller IRQx

input of the Root Port that is activated by this function’s

interrupt. The following encodings are defined:

• 6'h000000: IRQ0

• 6'h000001: IRQ1

• 6'h000002: IRQ2

• ...

• 6'h0000FF: unknown or not connected

Specify in Qsys

RO

Related Information

UG-01097_sriov

2014.12.15

Interrupt Line and Interrupt Pin Register

5-5

Registers

Altera Corporation