Power management capability structure – Altera Stratix V Avalon-ST User Manual

Page 84

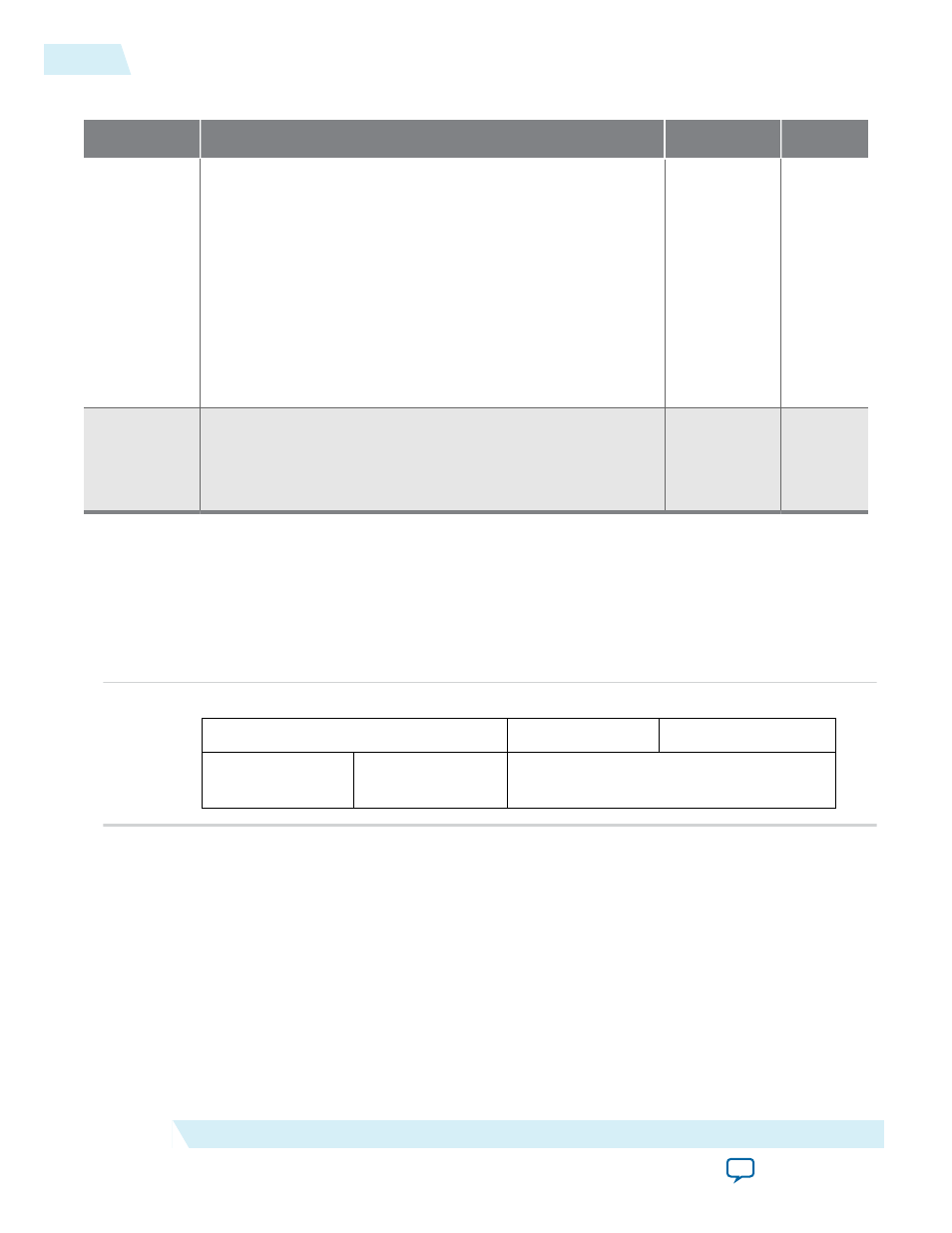

Table 5-11: MSI-X Pending Bit Array (PBA) Offset Register - 0x070

Bits

Register Description

Default Value

Access

[2:0]

MSI-X Pending Bit Array BAR Indicator. Specifies the BAR

number whose address range contains the Pending Bit Array

(PBA) table for this function. The following encodings are

defined:

• 3'b000: BAR0

• 3'b001: BAR1

• 3'b010: BAR2

• 3'b011: BAR3

• 3'b100: BAR4

• 3'b101: BAR5

Set in Qsys

RO

[31:3]

Specifies the memory address offset for the PBA relative to the

specified base address value of the BAR number specified in MSI-

X Pending Bit Array BAR Indicator, at [2:0] above. The address is

extended by appending 3 zeroes to create quad-word alignment.

Set in Qsys

RO

Related Information

Power Management Capability Structure

Figure 5-4: Power Management Capability Structure - Byte Address Offsets and Layout

0x078

0x07C

Capabilities Register

Next Cap Ptr

Data

31

24 23

16 15

8 7

0

Capability ID

Power Management Status and Control

PM Control/Status

Bridge Extensions

5-10

Power Management Capability Structure

UG-01097_sriov

2014.12.15

Altera Corporation

Registers