Altera Stratix V Avalon-ST User Manual

Page 6

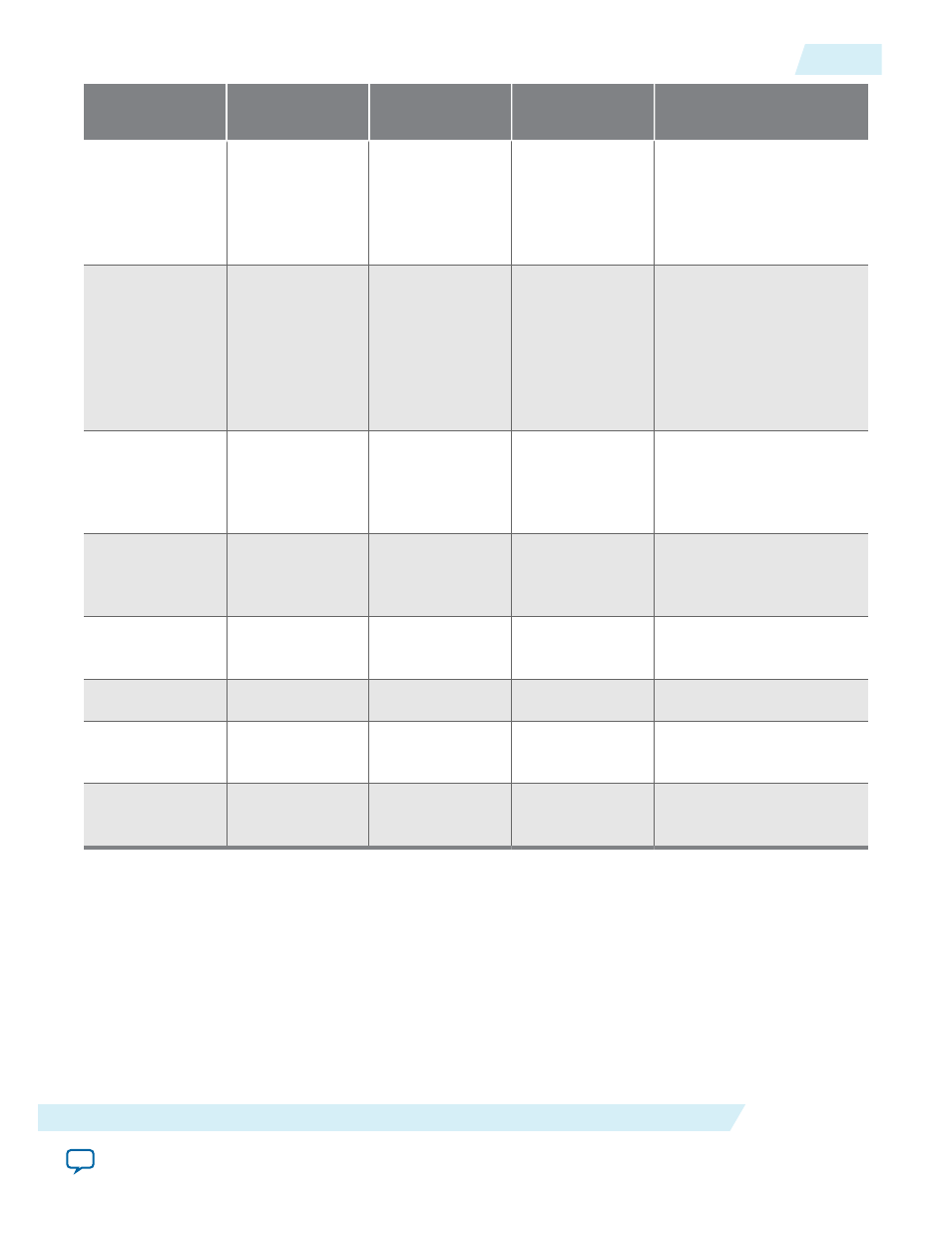

Feature

Avalon‑ST Interface

Avalon‑MM

Interface

Avalon‑MM DMA

Avalon‑ST Interface with SR-

IOV

Out-of-order

completions

(transparent to

the Application

Layer)

Not supported

Supported

Supported

Not supported

Requests that

cross 4 KByte

address

boundary

(transparent to

the Application

Layer)

Not supported

Supported

Supported

Supported

Polarity

Inversion of

PIPE interface

signals

Supported

Supported

Supported

Supported

ECRC

forwarding on

RX and TX

Supported

Not supported

Not supported

Not supported

Number of MSI

requests

1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 (for

Physical Functions)

MSI-X

Supported

Supported

Supported

Supported

Legacy

interrupts

Supported

Supported

Supported

Supported

Expansion

ROM

Supported

Not supported

Not supported

Not supported

The Stratix V Avalon-ST Interface with SR-IOV PCIe Solutions User Guide explains how to use this IP core

and not the PCI Express protocol. Although there is inevitable overlap between these two purposes, use

this document only in conjunction with an understanding of the PCI Express Base Specification.

Note: This release provides separate user guides for the different variants. The Related Information

provides links to all versions.

Related Information

•

•

•

UG-01097_sriov

2014.12.15

Features

1-5

Datasheet

Altera Corporation